#### Dipartimento di / Department of

| Fisi                                  | ca "Giuseppe Occhialini"           |                      |

|---------------------------------------|------------------------------------|----------------------|

| Dottorato di Ricerca in / PhD program | Fisica e Astronomia                | Ciclo / Cycle XXXIII |

| Curriculum in Fisica Subnucleare      | e e Tecnologie Fisiche - 86R -     | - 2                  |

|                                       |                                    |                      |

|                                       |                                    |                      |

| Integrated Circ<br>Technologies f     | uits Design in l<br>or Wireless Ap |                      |

|                                       |                                    |                      |

| Cognome / Surname Fary                | Nome / Name                        | Federico             |

| Matricola / Registration number 746   | 5961                               |                      |

|                                       |                                    |                      |

|                                       |                                    |                      |

| Tutore / Tutor: Prof. Andrea Base     | hirotto                            |                      |

|                                       |                                    |                      |

|                                       |                                    |                      |

|                                       |                                    |                      |

| Coordinatore / Coordinator: Pro       | of. Marta Calvi                    |                      |

|                                       |                                    |                      |

### **Contents**

| I  | Ab   | stract     |                                                                                      | 1  |

|----|------|------------|--------------------------------------------------------------------------------------|----|

| II | O    | vervie     | ew                                                                                   | 5  |

| 1  | Dov  | vn-Scal    | ling Trends in Deep-Submicron Technologies                                           | 9  |

|    | 1.1  | Backg      | round and Motivations                                                                | 9  |

|    | 1.2  | Impac      | ct of the Down-Scaling Process on MOS Transistor performances                        | 11 |

|    |      | 1.2.1      | Introduction: Supply and Threshold Voltage Scaling                                   | 11 |

|    |      | 1.2.2      | Figures-of-Merit for MOS performances evaluation                                     | 13 |

|    |      | 1.2.3      | Technology nodes and Test-Bench setup                                                | 14 |

|    |      | 1.2.4      | Bias Current vs Gate-Source Voltage                                                  | 15 |

|    |      | 1.2.5      | Bias Current vs Drain-Source Voltage                                                 | 20 |

|    |      | 1.2.6      | Planar vs FinFET Technology                                                          | 21 |

| 2  | Base | eband .    | Analog Filters and Variable Gain Amplifiers                                          | 25 |

|    | 2.1  |            | og Filters specifications for TLC applications                                       | 25 |

|    | 2.2  | Analo      | og Filters Topologies                                                                | 26 |

|    |      | 2.2.1      | Active-RC Analog Filters                                                             | 27 |

|    |      | 2.2.2      | Source-Follower based Analog Filters                                                 | 28 |

|    | 2.3  | Analo      | og Filters Figure of Merit                                                           | 29 |

| 3  | Acti | ve-RC      | Analog Filters Design                                                                | 33 |

|    | 3.1  | Rauch      | Biquadratic Cell Design                                                              | 33 |

|    |      | 3.1.1      | Rauch Biquadratic DC-Operating Point                                                 | 33 |

|    |      | 3.1.2      | Transfer Function, Noise and RC sizing                                               | 34 |

|    | 3.2  | $6^{th}$ O | rder $50 \text{ MHz} 18 \text{dBm-} IIP_3 \text{ Analog Filter with 7GHz Bandwidth}$ |    |

|    |      | OTA .      |                                                                                      | 34 |

|    |      | 3.2.1      | The 7GHz OTA Design                                                                  | 34 |

|    |      | 3.2.2      | Experimental Results                                                                 | 39 |

|    | 3.3  | $3^{rd}$ O | rder 60 MHz Analog Filter For 5G Full-Duplex Applications                            | 41 |

|    |      | 3.3.1      | 5G Full-Duplex VGA Design                                                            | 43 |

|    |      | 3.3.2      | Simulation Results                                                                   | 44 |

| 4  | Sou  | rce-Fol    | lower Analog Filters Design                                                          | 47 |

|    | 4.1  | The 4      | <sup>th</sup> Order Flipped-Source-Follower Filter                                   | 47 |

|    |      | 4.1.1      | Biquad Flipped-Source-Follower Cell Design                                           | 47 |

|    |      | 4.1.2      | Operating Point and Signal Swing                                                     | 48 |

ii CONTENTS

|    |            | 4.1.3     | Transfer Function                                                     |    |

|----|------------|-----------|-----------------------------------------------------------------------|----|

|    |            | 4.1.4     | Noise                                                                 | 50 |

|    |            | 4.1.5     | Measurement Results                                                   | 50 |

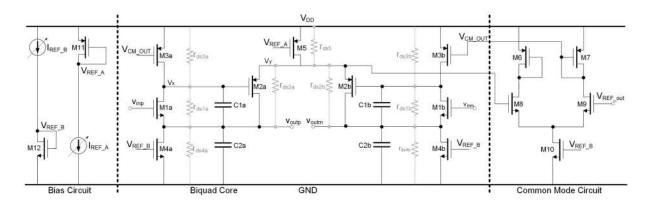

|    | 4.2        | The $4^t$ | $^{th}$ Order Fully-Differential Super-Source-Follower Filter $\dots$ | 53 |

|    |            | 4.2.1     | Operating Point and Signal Swing                                      | 55 |

|    |            | 4.2.2     | Transfer Function                                                     |    |

|    |            | 4.2.3     | Noise and Design Guidelines                                           |    |

|    |            | 4.2.4     | Simulation and Measurement Results                                    |    |

| 5  | Ana        | log Fili  | ter Designs Comparison with the State-of-the-Art                      | 63 |

| 0  | 5.1        | _         | parison with SoA                                                      |    |

|    | 0.1        | comp      | MISON WINI SOIL                                                       | 01 |

| II | I P        | apers     |                                                                       | 67 |

| 6  | Rela       | ated Pa   | pers                                                                  | 69 |

|    | 6.1        |           | ICICDT 2018                                                           | 70 |

|    | 6.2        | IEEE I    | ESSCIRC 2018                                                          | 74 |

|    | 6.3        |           | ESSCIRC 2019                                                          |    |

|    | 6.4        |           | ICECS 2019                                                            |    |

| 7  | Post       | ter       |                                                                       | 87 |

|    | 7.1        | IEEE I    | ICICDT 2018                                                           | 88 |

|    |            | _         |                                                                       |    |

| IV | 7 <b>C</b> | Conclu    | sions                                                                 | 91 |

| 8  | Con        | clusior   | าร                                                                    | 93 |

| Вi | bliog      | raphy     |                                                                       | 97 |

## **List of Figures**

| 1.1  | Moore's Law for Transistors' Number in a Single Integrated Circuit vs             | 0  |

|------|-----------------------------------------------------------------------------------|----|

| 4.0  | Manufacturing Year. Source: OurWorldinData.org                                    | 9  |

| 1.2  | $V_{DD}$ & $V_{TH}$ (a) and $V_{DD}$ - $V_{TH}$ (b) vs Minimum Channel Length     | 12 |

|      | (a)                                                                               | 12 |

|      | (b)                                                                               | 12 |

| 1.3  | $I_{DS}$ vs Overdive Voltage $(V_{GS} - V_{TH})$ for different technology nodes . | 15 |

| 1.4  | Transconductance vs Overdive Voltage $(V_{GS} - V_{TH})$ for different tech-      |    |

|      | nology nodes                                                                      | 16 |

| 1.5  | Transistor Efficiency vs Overdive Voltage $(V_{GS} - V_{TH})$ for different       |    |

|      | technology nodes                                                                  | 17 |

| 1.6  | Gate Capacitance $C_{GS}$ vs Overdive Voltage $(V_{GS} - V_{TH})$ for different   |    |

|      | technology nodes                                                                  | 18 |

| 1.7  | Transistion Frequency $f_T$ vs Overdive Voltage $(V_{GS} - V_{TH})$ for different |    |

|      | technology nodes                                                                  | 19 |

| 1.8  | Efficiency-Transition Frequency product vs Overdive Voltage ( $V_{GS}$ –          |    |

|      | $V_{TH}$ ) for different technology nodes                                         | 19 |

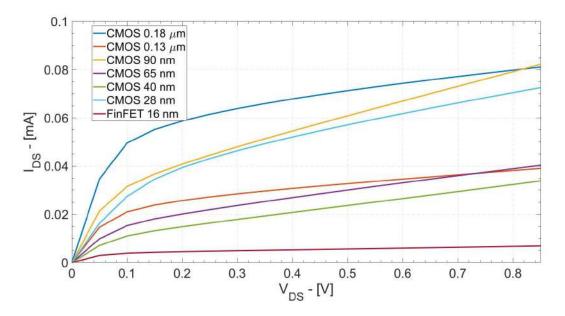

| 1.9  | $I_{DS}$ vs $V_{DS}$ for different technology nodes                               | 20 |

| 1.10 | Transistor Intrinsic Gain $(gm/g_{DS})$ vs $V_{DS}$ for different technology      |    |

|      | nodes                                                                             | 21 |

| 1.11 | FinFET MOS Transistor device scheme                                               | 22 |

| 1.12 | FinFET MOS Transistor Gate Capacitance Scheme                                     | 23 |

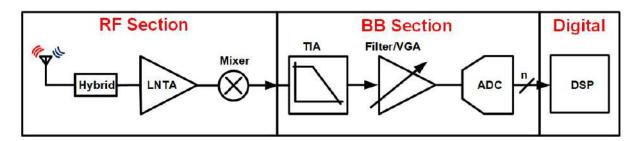

| 2.1  | TLC Receiver basic building blocks scheme                                         | 25 |

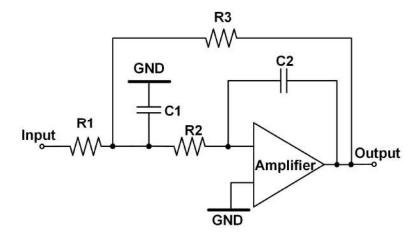

| 2.2  | Active-RC Filter: Rauch Biquadratic cell                                          | 28 |

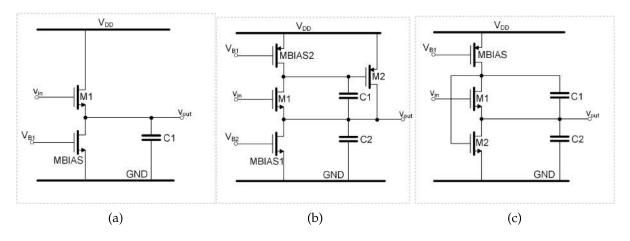

| 2.3  | Source-Follower (a), Super-Source-Follower (b) and Flipped-Source-                |    |

|      | Follower (c) Scheme                                                               | 29 |

|      | (a)                                                                               | 29 |

|      | (b)                                                                               | 29 |

|      | (c)                                                                               | 29 |

| 3.1  | 7 GHz OTA Active-RC filter scheme                                                 | 35 |

| 3.2  | 7 GHz OTA Transistor Level Scheme                                                 | 36 |

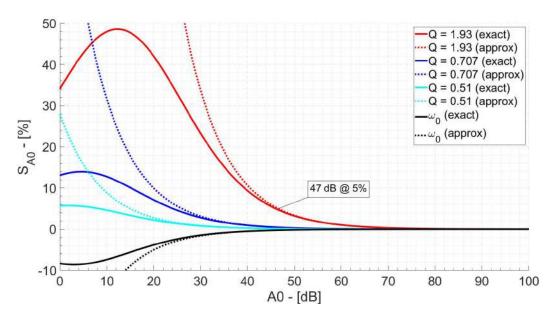

| 3.3  | Quality Factor and Poles Frequency Sensitivities vs OTA DC-Gain                   | 37 |

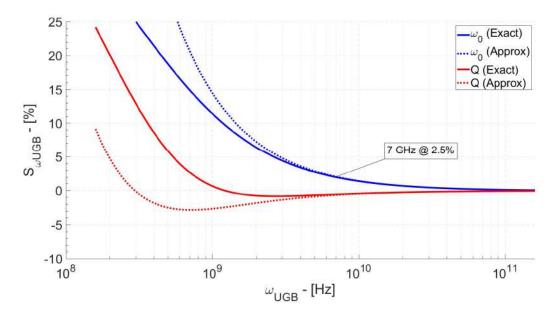

| 3.4  | Quality Factor and Poles Frequency Sensitivities vs OTA $\omega_{UGB}$            | 37 |

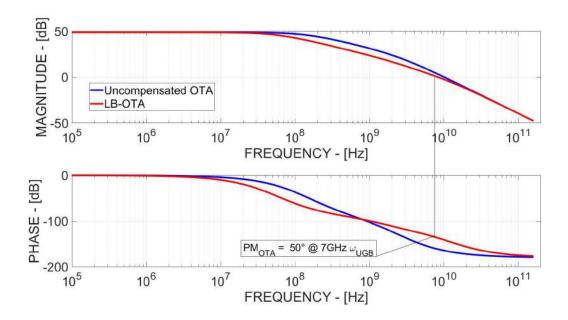

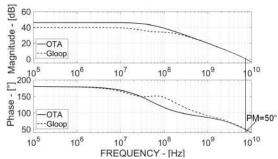

| 3.5  | 7GHz OTA Frequency Response VS Uncompensated OTA                                  | 38 |

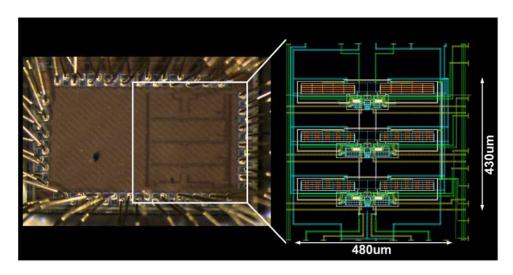

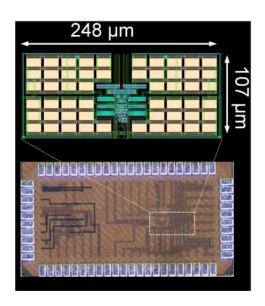

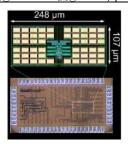

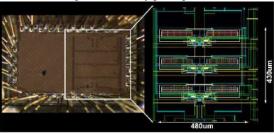

| 3.6  | Prototype and Layout photo                                                        | 39 |

|      |                                                                                   |    |

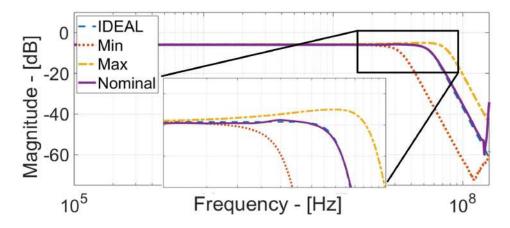

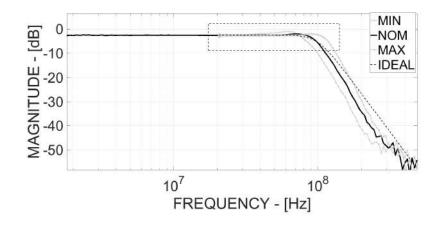

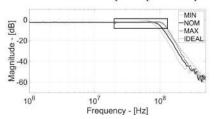

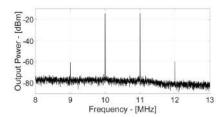

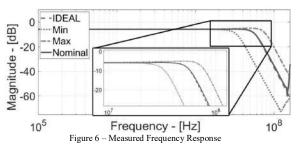

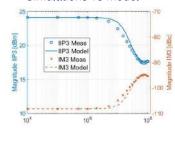

| 3.7  | Measured Frequency Response                                              | 40 |

|------|--------------------------------------------------------------------------|----|

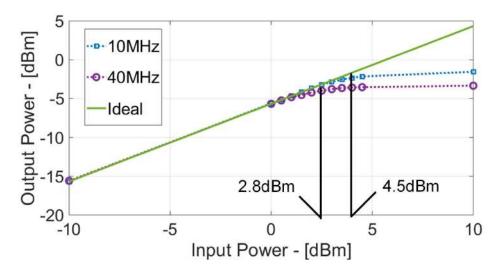

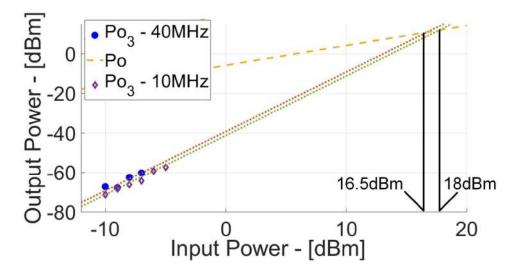

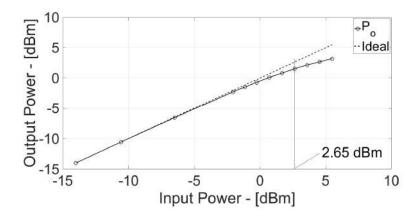

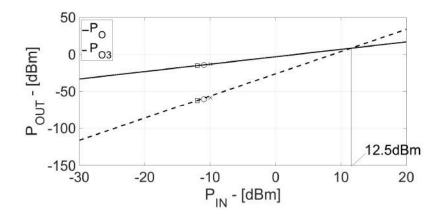

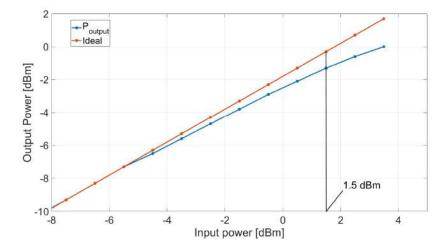

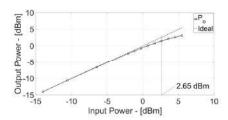

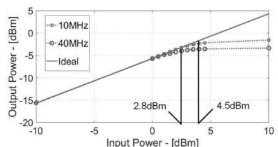

| 3.8  | 1dB Compression Point 10MHz and 40MHz                                    | 41 |

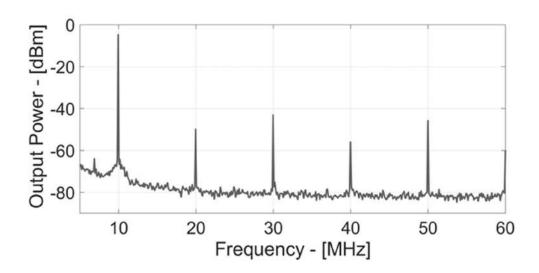

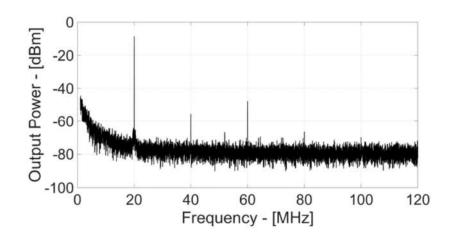

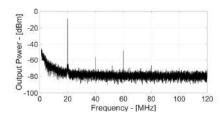

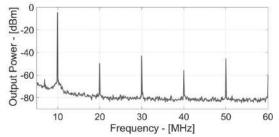

| 3.9  | Output spectrum with 20MHz Input Signal                                  | 41 |

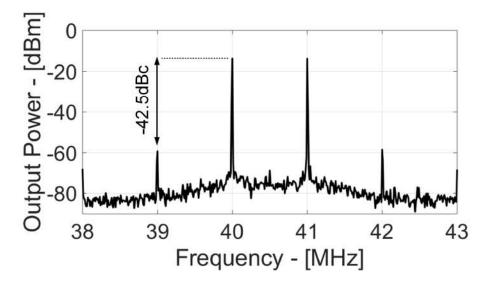

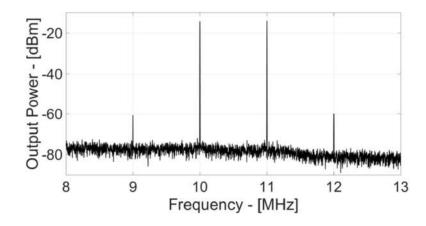

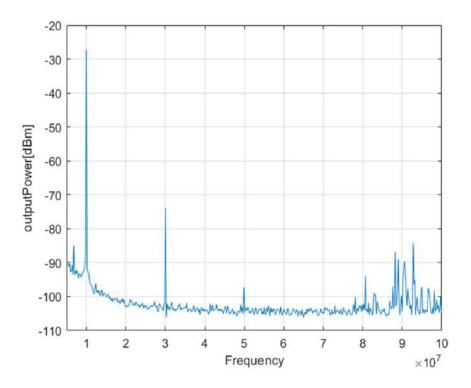

| 3.10 | Output Spectrum @ 40 & 41 MHz Input Signal                               | 42 |

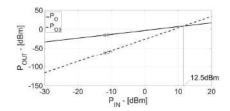

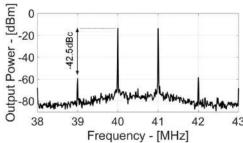

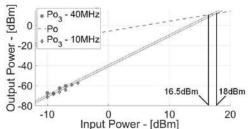

| 3.11 | IIP3 at 10&11MHz and 40&41MHz Input Signals                              | 42 |

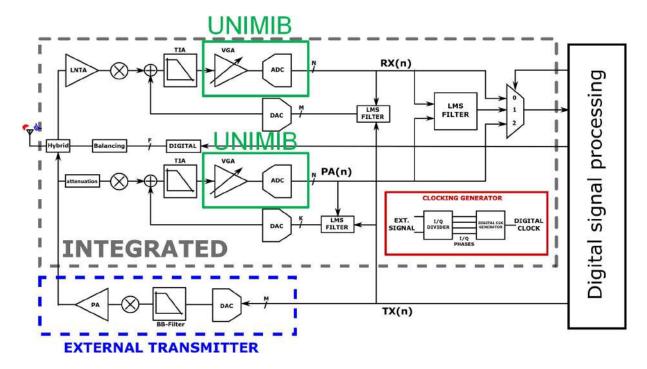

| 3.12 | Full-Duplex Building Blocks Scheme                                       | 43 |

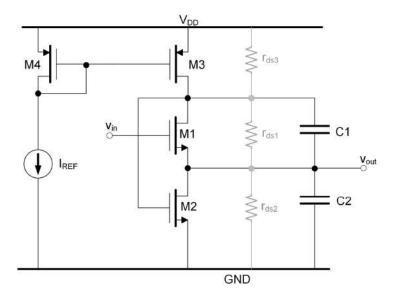

| 3.13 | Variable Gain Amplifier Scheme                                           | 44 |

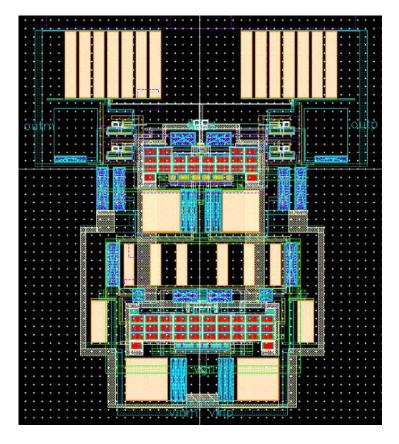

|      | Variable Gain Amplifier Layout photo                                     | 45 |

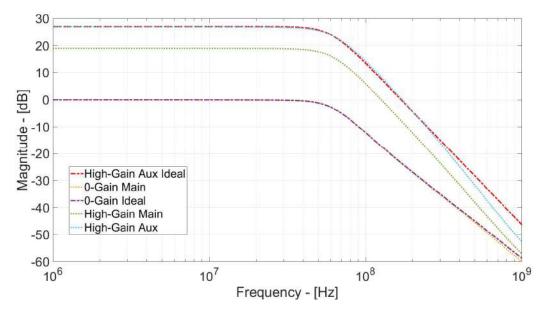

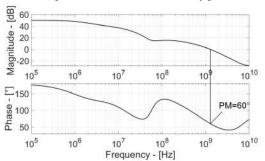

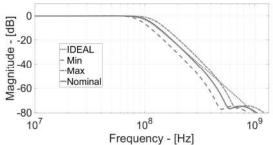

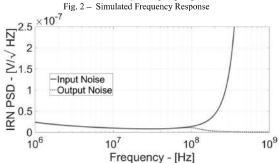

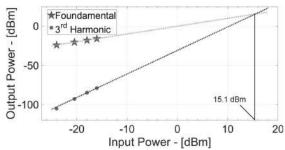

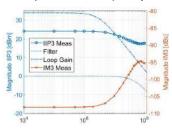

|      | Simulated Frequency Response                                             | 45 |

| 4.1  | NMOS Flipped-Source-Follower Biquadratic Cell                            | 48 |

| 4.2  | Flipped-Source-Follower $4^{th}$ Order Filter – Single-Ended Branch      | 50 |

| 4.3  | Chip and Layout Photo                                                    | 51 |

| 4.4  | Whole Bandwidth Frequency Response                                       | 51 |

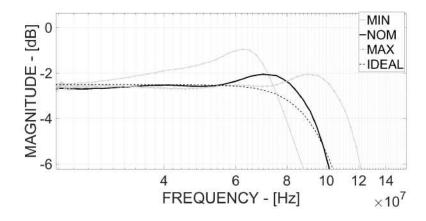

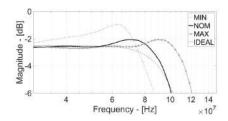

| 4.5  | Bandwidth Edge Frequency Response                                        | 52 |

| 4.6  | 1dB Compression Point with one tone at 10MHz                             | 53 |

| 4.7  | Output Spectrum with 20MHz Input Signal                                  | 53 |

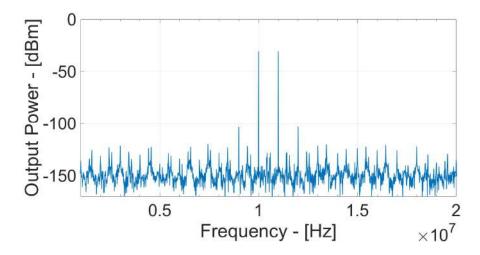

| 4.8  | Output Spectrum with 10&11MHz Input Signal                               | 54 |

| 4.9  | IIP3 at 10&11MHz Input Signal                                            | 54 |

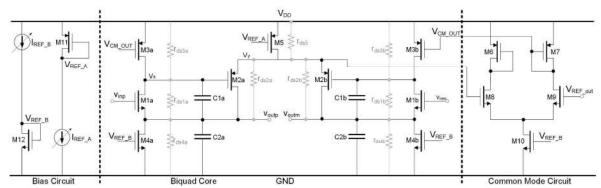

| 4.10 | Fully-Differential Super Source Follower N-cell Schematic                | 55 |

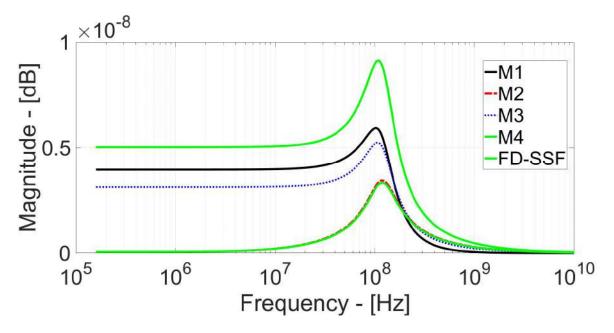

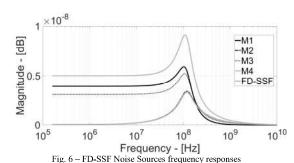

| 4.11 | FD-SSF Noise Sources frequency responses                                 | 58 |

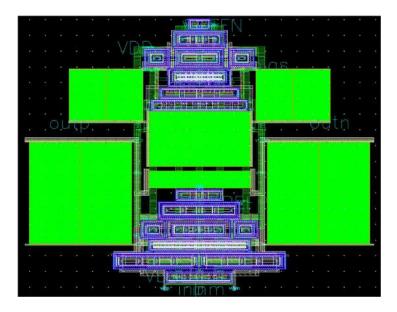

|      | FD-SSF Layout                                                            | 59 |

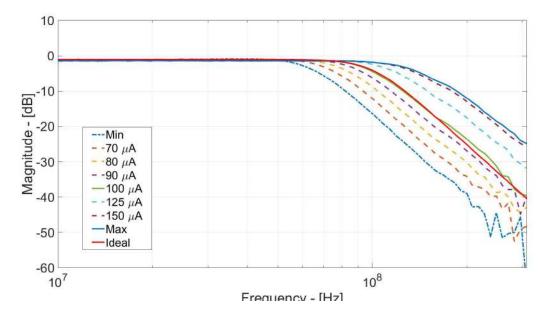

|      | Measured Frequency Response and tunability                               | 60 |

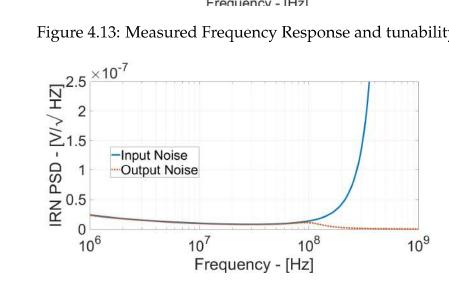

|      | Simulated Input-Referred Noise Power Spectral Density                    | 60 |

|      | 1 dB Compression Point with one tone @ 10 MHz                            | 60 |

|      | Output Spectrum with 10 MHz Input Signal                                 | 61 |

|      | Output Spectrum with 2 tones at 10&11 MHz                                | 62 |

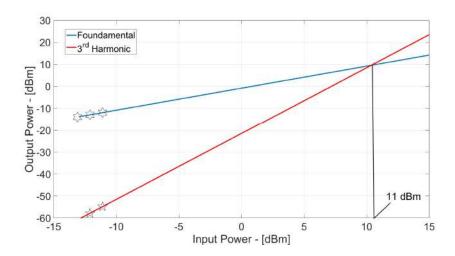

|      | IIP3 reference curves for 2 tones @ 10& MHz                              | 62 |

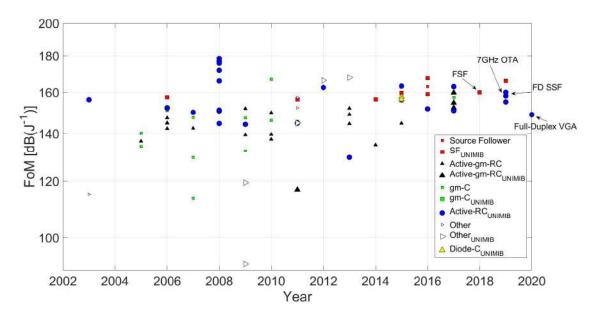

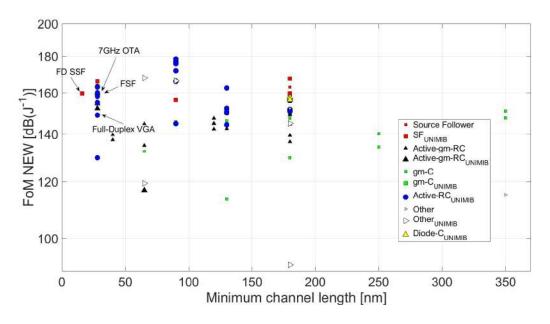

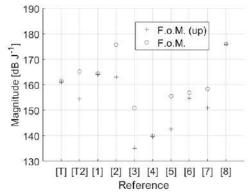

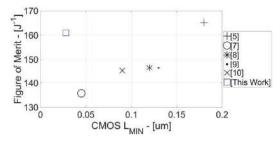

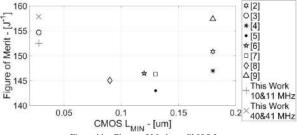

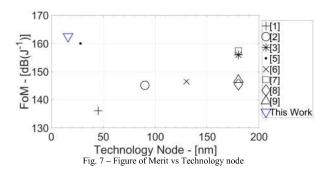

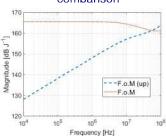

| 5.1  | Figure of Merit vs Manufacturing Year for different Filter Architectures | 65 |

| 5.2  | Figure of Merit vs Technology node for different Filter Architectures .  | 65 |

### **List of Tables**

| 2.1 | Analog Filters Specifications          | 26 |

|-----|----------------------------------------|----|

| 3.1 | Filter Specifications                  | 35 |

| 3.2 | Rauch Biquad Design Parameters         | 35 |

| 3.3 | Rauch Biquad Design Parameters         | 39 |

| 3.4 | Filter Performance Resume              | 40 |

| 3.5 | Variable Gain Amplifier Specifications | 43 |

| 3.6 | Variable Gain Amplifier Specifications | 46 |

| 4.1 | Filter Specifications                  | 51 |

| 4.2 | Filter Performances                    |    |

| 4.3 | Filter Parameters and specifications   | 55 |

| 4.4 | Filter Performances                    | 62 |

| 5.1 | Filters Performances Resume            | 63 |

# Part I Abstract

#### **Abstract**

In the last 30 years, Mobile Telecommunication (TLC) electronics proved to be one of the major driving motor in the development of new Complementary Metal-Oxide-Semiconductor (CMOS) technologies. This limited branch of the electronics world managed to move billions of dollars worldwide, some of which unavoidably ended up in financing advanced research projects to answer market demands. People all around the world ask for extremely performing portable devices, faster, more reliable, low power consuming and with impressive memory capability. To answer all these requests, physics and engineers developed new and incredibly down-scaled technology nodes, which met the high speed and low power consumption requirement, granting an impressive circuital density.

Nowadays foundries such as TSMC or Samsung are able to manufacture incredibly small transistor devices, with channel length in the order of only 7 nm and transition frequency in the order of several hundreds of GHz. This situation has become extremely favorable for the development of high performance digital devices, which are able to reach speed and memory capability previously unbelievable. Nonetheless, also analog building blocks must be integrated in deeply down-scaled node, in order to adapt with digital ICs.

First task of this thesis work is to develop analog ICs in deep sub-micron technology nodes, such as 28 nm bulk-CMOS and 16 nm FinFET (Fin Field Effect Transistor). This has been accomplished facing several difficulties given by the very poor analog behavior of such advanced technologies, especially in terms of low transistor intrinsic gain and limited signal headroom, caused by the low supply voltage.

The second task of this work is to develop these same analog ICs in order that they meet requirements of the most advanced TLC standards, such as LTE and 5G. The increased number of portable devices worldwide made in fact unavoidable the introduction of new communication standards, in order to face the huge number of connected devices. This work presents 4 building blocks that can be exploited in every next generation transceiver device. In detail, this work analyzes though extended simulations and measurements 3 Base-Band analog filters and 1 variable gain amplifier, suitable for 5G applications. These designs have been developed in 28nm CMOS and 16 nm FinFET. Each design shows the most important difficult that was faced for its realization and highlight the most important performances of every prototype device, with an extensive confrontation with the State-of-the Art.

The first device is a  $6^{th}$  Order Rauch based analog filter, which exploit a large bandwidth amplifier to achieve low quality factor sensitivity and high linearity performances. The second is a  $3^{rd}$  order variable gain amplifier, with low noise and high linearity performances, suitable to be integrated in a Full-Duplex 5G transceiver Base-

Band section. The third and fourth devices are source follower based  $4^{th}$  order filters with very low noise and low power performances. One exploit the Flipped-Source-Follower architecture, while the second integrates an innovative Fully-Differential Super-Source-Follower topology. This last design also exploit the advanced FinFET technology, which shows better intrinsic gain, in order to maintain high linearity performances, despite the Fully-Differential configuration.

# Part II Overview

#### **Overview**

Task of this thesis work is to deal with analog Integrated Circuits (ICs) which find applications in nowaday most advanced Telecommunication (TLC) Systems-on-Chip (SoC). Pushed by more speed and low power consumption requirements, usually such systems rely on advanced technology nodes, which tend to guarantee high performances, especially for SoC digital sections, which are assuming, over the years, more and more relevance in every system design. However, analog sections, Radio-Frequency (RF) and Base-Band (BB), usually suffer from performance degradation because of the technology downscaling process, forcing analog designers to find new circuital topologies and architectures to meet the most advanced standards requirements.

This work proposes several IC solutions for TLC analog baseband section, that also fit requirements of the most advances TLC standards (LTE and, especially, 5G). At the same time, they exploit the most advanced technology nodes, such as 28 nm CMOS (Bulk) and 16 nm FinFET (Bulk) to apply with the digital section. This thesis covers one of the analog baseband most important building blocks: the Filter/VGA. In detail, two different baseband analog filter topologies are here analyzed (for an overall count of 4 different prototype devices). 3 Prototypes are intedrated in 28nm CMOS technology and 1 in 16 nmFinFET.

This thesis is organized into 8 different chapters, as follows.

A brief introduction of the entire work can be found in **Chapter 1**. This section set the most important tasks of this work, illustrates the most important trends in the downscaling process and provides valuable information about differences between CMOS and FinFET technologies.

Chapter 2 is dedicated to the description of the two analog filter architectures exploited through this work, the Active-RC and the Source-Follower based. The here presented theoretical analysis is followed in Chapter 3 and Chapter 4 by a complete set of measurement on several prototype devices integrated in different technology nodes, that validates the main ideas behind their designs. Overall performances are then compared in Chapter 5 with the State-of-the-Art by the help of a newly introduced Figure of Merit.

Correlated pubblications can be found in **Chapter 6** and related Poster in **Chapter 7**.

In Chapter 8 conclusions will be drawn.

#### 1

## Down-Scaling Trends in Deep-Submicron Technologies

#### 1.1 Background and Motivations

In the last 30 years, Systems-on-Chip (SoC) for mobile Telecommunications (TLC) have proved to be the major driving motor for the development of new technology nodes and for the extend of the Complementary Metal-Oxide-Semiconductor (CMOS) scaling. Financially speaking, this "tiny" portion of the wide world of electronics gained larger and larger space in the economic markets, moving, nowadays, huge amount of money, in the order of tenths of billions of dollars. For this reason, it is not difficult to guess why research on mobile devices imposes itself as a very leading force in the technology down-scaling process. In detail, the development of smaller and smaller technology nodes allows to integrate an ever-greater number of more performing Integrated Circuits (ICs), faster and more efficient, in a same silicon area, increasing the final device performances and responding to market demands.

Price of a silicon run in "older" (i.e less scaled) technologies unavoidably reduces

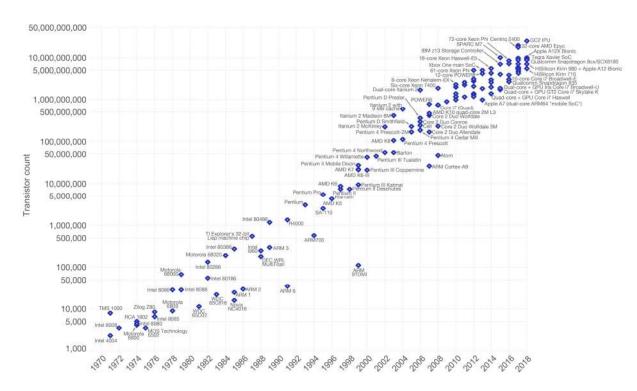

Figure 1.1: Moore's Law for Transistors' Number in a Single Integrated Circuit vs Manufacturing Year. Source: OurWorldinData.org

when a new node is introduced, while technological innovations are intrinsically more expensive (i.e. hundreds of thousands euros for few  $mm^2$  in 16 nm FinFET, while the same area in planar CMOS 28 nm can be bought today for few thousand euros, just few hundreds euros in 180 nm and so on). On the other hand, the most advanced technology nodes allow to integrate a larger number of ICs in a same silicon run, with an exponentially larger efficiency and reliability. As a consequence, a top-level final product (mobile phone, smartphone, tablet, etc...) will have almost the same cost through the generations, but with significantly larger speed performances and processing capability.

For instance, technology down-scaling process allows Apple Inc. to move from its A7 processor, which fit in the 2011 iPhone 5s, with "only" 1 Billion transistors and manufactured in 28 nm CMOS (from Samsung), to the A12 processor which fit in the 2018 iPhone 10X, manufactured in 7 nm FinFET technology (from TSMC) and with 10 times more transistor. Both products have almost the same price at their release date, but with impressively increased performances one from the other. This is, of course, an application of the well-known Moore's law for electronics (figure 1.1) [1]) which states that the number of transistors for a given area doubles every 18 months and the cost of a single transistor decreases as IC density increases. Even if we are now moving to an era called "beyond Moore's Law", where these two axioms are starting to lose their truthfulness [2], it is nevertheless true that the reduced cost of the single transistor allows production of low-end portable devices that almost everybody around the world can afford. This situation led to an exponential increase in the number of smartphones and tablets that needs to be connected to the Web all around the world, increasing the complexity and the number of connections that each Base-Station must handle. This situation results in the need for new TLC standards (4G, LTE and, in the last years, 5G) that allow to manage the increased demand for data bandwidth, through the extension of transmission frequencies and single channels width. To apply in an efficient way with these new standards, it is necessary to review each transceiver hardware, making it compatible with the new era to come.

These are the two challenges that this three years' work had to face. On one hand, there is the need of realizing analog ICs compatible with the most advanced TLC standards, and especially suitable for 5G applications. On the other hand, it was necessary to face the issues of the most advanced technologies. In fact, the new proposed architectures will have to achieve high speed and low power performances, such that they can be exploited on mobile electronics, and, moreover, they will have to be integrated in scaled technology nodes, such that they can apply, in Mixed-Signals SoC, with the already optimized digital sections.

For these reasons, task of this thesis work is to realize analog building blocks, filters and amplifiers, for TLC systems in Deep-Submicron technologies, facing their most important limitations while exploiting their large advantages [3], realizing high performances devices, suitable for the most advanced 5G standard.

## 1.2 Impact of the Down-Scaling Process on MOS Transistor performances

#### 1.2.1 Introduction: Supply and Threshold Voltage Scaling

Task of this paragraph is to focus on the most important MOS analog performances trends that follows the down-scaling process. The difference between analog and digital performances is crucial in this analysis, since they are especially the second ones that define some of the characteristic parameters of a technology node, such as supply voltage ( $V_{DD}$ ) and/or threshold voltage ( $V_{TH}$ ), while the first ones usually must adapt accordingly. It is known, in fact, that IC supply voltage decrease with decreasing transistors minimum channel length (i.e. the technology node) in order to guarantee an acceptable power dissipation density per area unit while devices density increases (this is related to the substrate maximum thermal dissipation). This situation is very favorable for digital IC, where logic gate dynamic power consumption  $P_{Dyn}$ , which is commonly the most important contribution to the overall power consumption, is related to the supply-voltage by the well-known equation:

$$P_{\rm Dyn} = C \times \text{freq} \times V_{\rm DD}^2 \tag{1.1}$$

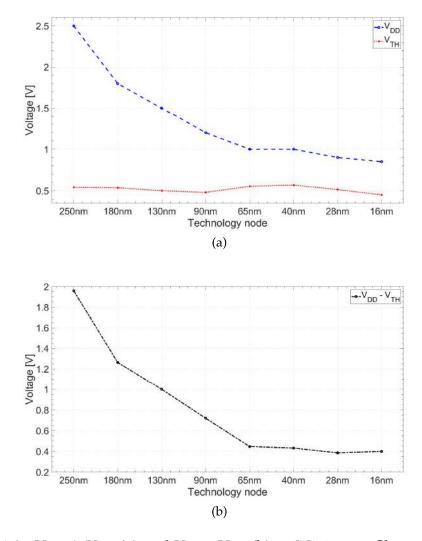

where C is the load capacitance and freq is the switching frequency. Moreover, standard MOS threshold voltage used to decrease with the technology scaling-down, until 90 nm, but not as fast as the supply voltage. In most recent nodes,  $V_{TH}$  remains almost constant, coming back to a decreasing trend only with the introduction of the FinFET technologies [4]. In figure 1.2 (a), the  $V_{DD}$  and  $V_{TH}$  trends versus technology nodes (expressed as transistor minimum channel length) previously described are clearly reported. As for the  $V_{DD}$ , this  $V_{TH}$  trend [5] allows to maintain a low power consumption in digital applications, since the threshold voltage is related to the off-state transistor leakage current[6]-[7]-[8],  $I_{OFF}$  as described in [9]. This subthreshold current appears between source and drain when the MOS is biased with a gate voltage well below the threshold voltage and can be expressed as in [10]:

$$I_{OFF} = I_0 \frac{W}{L_{eff}} \left(\frac{kT}{q}\right)^2 e^{\frac{-V_{TH} + \eta V_{DD}}{n\frac{kT}{q}}}$$

(1.2)

where  $I_0$  is a technology dependent constant (related to carrier mobility and gate-oxyde capacitance), W and  $L_{eff}$  are transistor width and effective channel length, T is the temperature, k is the Boltzmann constant, q is the electron charge, n is the sub-threshold slope and  $\eta$  is the Drain-Induced Barrier Lowering (DIBL) coefficient [11]. From equation 1.2 it is possible to infer that  $V_{TH}$  can not further reduce without a significant increase in this leakage current and so an increase in the overall digital device power consumption [12]. The introduction of the FinFET technology in sub-20nm nodes allows a better control of the conductive channel thanks to the 3-dimensional gate that completely surround the channel substrate itself. This translates in a leakage

Figure 1.2:  $V_{DD}$  &  $V_{TH}$  (a) and  $V_{DD}$  -  $V_{TH}$  (b) vs Minimum Channel Length

current reduction that allows a slight decrease of the threshold voltage.

In figure 1.2b, the difference  $V_{DD}-V_{TH}$  is also reported. As it can be noticed, technology downscaling led to a reduction in the difference between supply voltage and threshold voltage down to only 400 mV. This situation is not a disadvantage for digital application, while it is critical in analog IC, since it is not possible to bias transistors with large Overdrive Voltage ( $V_{OV}$ , defined as the difference between gate-source voltage and threshold voltage and limited to  $V_{DD}-V_{TH}$ ). This situation causes several disadvantages in analog applications, such as:

- transistor must be biased in subthreshold/weak inversion region, where the exponential characteristic makes devices less linear and the reduced transconductance (*gm*) increases transistor thermal noise.

- Transistor output signal swing is limited.

- It is extremely difficult and sometimes impossible to realize cascade topologies.

#### 1.2.2 Figures-of-Merit for MOS performances evaluation

Given these first considerations, it is necessary to define criteria and parameters, from now on called Figure-of-Merit (FoM), which allows a fair performances analysis through the different technology nodes. This is not an easy task, since an analog performances accurate analysis must cover a broad range of biasing conditions, and generally requires high accuracy. For this reason, using mean-squared-error criteria in fitting current–voltage (I–V) and charge–voltage (Q–V) curves, across a wide range of bias conditions and "process corners" (such as in digital applications) is neither sufficient nor optimal for analog circuit design [13]. In an effort to make part of this work a continuation for [13] and [14], in this thesis these works are extended to deep-submicron technologies down to the 28 nm bulk-CMOS and 16 nm bulk-FinFET, the most advanced available for academic researches. Obviously, these are completely different technology one from the other, the first is planar while the other is 3-dimensional, and of course the appropriate considerations will be made while analyzing each performance and resumed at the end of this chapter.

It is now mandatory to define some criteria to be check in order to create these FoMs. First of all, it is necessary to define the transistor performances analog designer are more interest in. Basically, they can be reduced to only 4: bandwidth, noise, power consumption and voltage gain. These can be combined one with the others in order to obtain one or two FoMs that allow analog designers, at a first glance, to understand which technology node is the most suitable for a certain application and which is the most appropriate biasing region in which a transistor is most performant. These performances first need to be associated to MOS characteristics that can be physically measured.

Transistor Bandwidth is historically associated to the MOS Transition Frequency  $(f_T)$ , defined as:

$$f_{\rm T} = \frac{\rm gm}{2\pi C_{\rm gg}} \tag{1.3}$$

in which it is possible to recognize the transconductance gm and the gate Capacitance  $C_{gg}$ . Higher Transition Frequencies can be exploited by faster devices in RF applications.

Transistor noise is usually associated with its transconductance gm, while power consumption is associated with its DC Drain-Source Current  $I_{DS}$ . Usually, this two parameters, noise and power consumption, combine to the so-called transistor Efficiency Eff, defined as:

$$Eff = \frac{gm}{I_{DS}}$$

(1.4)

This parameter identifies the efficiency of a MOS in each technology node, i.e. how much power must be allocated for a given gm, or, better, for a given noise budget. Viceversa, it can be exploited to estimate the maximum noise of a device for a specific power budget. It is possible to further combine Efficiency and Transition Frequency in

a last FoM, called Band-Efficiency, by multiplying the two performances; the obtained FoM includes, in this way, noise, power consumption and bandwidth.

Being related to the transistor transconductance, this Figure-of-Merit depends on the MOS biasing point and, in particular, its characteristic is very different when the MOS is in sub-threshold or in strong-inversion region. The gm, in fact, assumes two different behavior versus the overdrive voltage:

- In Sub-Threshold is proportional to the square of the Overdrive Voltage.

- In Strong-Inversion is linear with the Overdrive Voltage untill it saturates.

For this reason, it is necessary to plot this FoM of merit as a graph versus the Overdrive Voltage, in order to understand which technology is the most performant in each biasing condition.

The last FoM is the Intrinsic Gain,  $A_i$ , related to the MOS voltage gain and defined as:

$$A_{i} = \frac{gm}{gds} \tag{1.5}$$

where gds is the transistor output conductance. In this case, gds is a function of the Drain-Source Voltage and for this reason an accurate analysis of the intrinsic gain must account for Drain and Source biasing point.

#### 1.2.3 Technology nodes and Test-Bench setup

Task of this section is to analyze and compare transistor performances, in different technology nodes, with the help of the previously mentioned Figures-of-Merit. In this way, it is possible to focus the attention on the most important advantages and disadvantages of the technology downscaling and of a technology over the others. Technologies considered in this work are:

- 180nm bulk-CMOS, the first with a gate length shorter than the wavelength of the light used for lithography;

- 130nm bulk-CMOS, the first to exploit low-k copper interconnects;

- 90nm bulk-CMOS, the first to exploit immersion lithography for its realization;

- 65nm bulk-CMOS, the first to exploit both copper interconnects and low-k dielectrics [15];

- 40nm bulk-CMOS, the first to exploit both immersion lithography and ultralow-k connection materials [16];

- 28nm bulk-CMOS, the first to exploit High-k Metal Gate (HKMG) [17] and gate-last process (instead of gate-first process)

• 16nm bulk-FinFET, the first commercialized Fin Field-Effect Transistor based technology.

For each of these technologies, two different test-bench setups have been realized. In the first, a minimum channel length transistor with an aspect ratio W/L=10 was biased with 0 V source and bulk voltage and drain voltage as high as the specific supply voltage of the technology considered. The gate voltage was swept between 0V and  $V_{DD}$ , while output current and other interesting performances were plotted versus the Overdrive voltage. In the second, the same minimum length MOS, with an aspect ratio of 10, was biased with a gate voltage 100 mV above the technology specific threshold voltage. The drain voltage was swept between 0V and supply voltage and outputs were plotted versus the drain voltage itself.

#### 1.2.4 Bias Current vs Gate-Source Voltage

This sub-section is dedicated to the analysis of those performances which are dependent on the gate-source Voltage ( $V_{GS}$ ), exploiting the first test-bench setup described in the previous section.

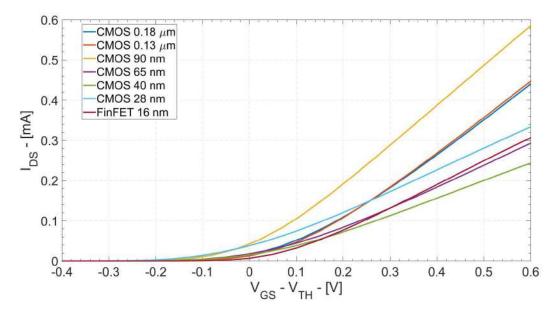

First of all, in figure 1.3, the  $I_{DS}$  versus  $V_{GS}$  (expressed as Overdrive voltage

Figure 1.3:  $I_{DS}$  vs Overdive Voltage  $(V_{GS} - V_{TH})$  for different technology nodes

in order to normalize to the threshold voltage which is peculiar of each technology) characteristic curves are plotted for each of the considered technology nodes, which can be identified by their minimum channel length. This plot allows to have a general idea about power consumption of a minimum channel length transistor while the technology node changes and, moreover, it allows to obtain transconductance curves, since gm is defined as:

$$g_{\rm m} = \frac{\partial I_{\rm DS}}{\partial V_{\rm GS}} \tag{1.6}$$

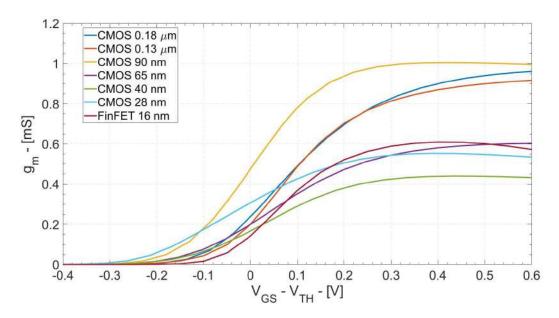

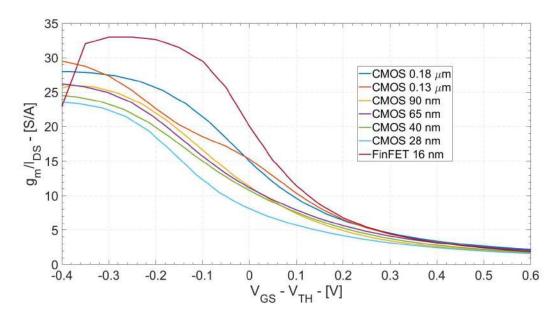

whose characteristic curve versus the overdrive voltage is reported in figure 1.4 for each different technology.

It is very difficult from 1.3 to find out a peculiar trend connected to the down-

Figure 1.4: Transconductance vs Overdive Voltage  $(V_{GS} - V_{TH})$  for different technology nodes

scaling process. This is mostly related to the large differences in the technology specific parameters, such as carrier mobility, gate oxide capacitance and pinch-off factor, which seems not to follows particular trends but are strongly dependent on the technology manufacturing characteristics. On the other hand, from figure 1.4, a trend in the gm variation seems to show up, especially in strong-inversion region, with the transconductance that reduces with technology scaling-down. 28nm and 90nm nodes seem not to follow this trend, but their particular behavior can be explained by the larger current, mostly leakage current, that shows up when the gate voltage is around 200mV below the threshold voltage. Especially in 28nm Bulk-CMOS technology, transistor shrinking led to a strong reduction in the capability of the gate voltage to properly control carrier in the conductive channel and this situation originates a leakage current contribution to the overall drain current which is not negligible as in other technology nodes. But if on one hand this increases power consumption in 28nm, on the other hand it allows more transconductance at low  $V_{GS}$  (i.e. 0.2 mS at  $V_{GS} = 400$  mV for a minimum length transistor, while the same gm is achieved in 180nm at  $V_{GS}$  = 500mV). This means that it is possible to get very good noise performances even though the supply voltage in this technology node is very limited and it is sometimes difficult to bias transistor with a large  $V_{GS}$ . This consideration applies for each technology with a comparable threshold voltage and for this reason this does not apply for the 16 nm FinFET. In this case in fact, the  $V_{TH}$  is 100 mV below the 28 nm threshold voltage, meaning that in both technology node it is possible to

achieve the same noise performances with the same biasing point, with almost the same power consumption.

From the characteristics in figure 1.3 and 1.4 it is possible to obtain transistor efficiency, which is plot in figure 1.5. In this plot it is possible to recognize, as a leading trend,

Figure 1.5: Transistor Efficiency vs Overdive Voltage  $(V_{GS} - V_{TH})$  for different technology nodes

a transistor efficiency reduction, very small actually in strong-inversion region, but larger in sub-threshold, with the technology down-scaling. For planar technologies in fact, a 600% reduction in minimum channel length, between 180nm and 28nm, translates in a lost of efficiency of roughly a 15% in weak-inversion region. This result must be carefully taken in consideration. It is true in fact that efficiency worsen in most recent nodes, but it is necessary to underline that in older technology transistors were usually biased in strong inversion region, with large overdrive voltage, exploiting the larger difference between supply voltage and threshold voltage. This allowed to achieve larger linearity performances, since the MOS operated where its characteristic curve  $I_{DS}$  vs  $V_{GS}$  is quadratic and not exponential as in sub-threshold, lower noise, thanks to the larger transconductance, but very high power consumption, because of the reduced efficiency in this operating region. The limited 28nm voltage headroom, forces MOS to be biased in weak-inversion/sub-threshold region allowing the exploitation of the larger efficiency of this region to realize low power devices and minimizing the impact of the reduced supply voltage on the overall performances.

As it is possible to notice from the same figure 1.5, FinFET technology is the only exception. In this case trend is reversed and the transconductance amount which can get for power consumption unit increases up to the 25% compared to the previous 28nm node, reaching 33 S/A for a minimum length sub-threshold transistor. This turnaround can be explained with the increased control over the conductive channel: lower leakage current means that more power consumption is exploited to generate

transconductance.

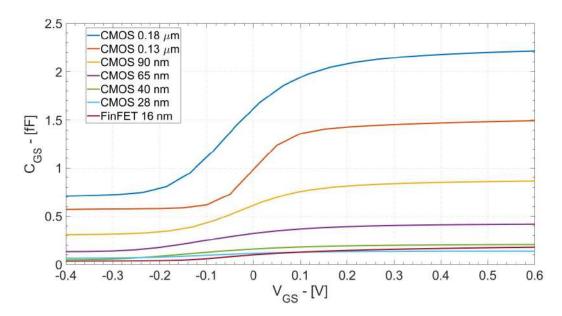

For what it concerns transistors transition frequency, the down-scaling trend is oriented, of course, to an increase in device speed. This is mostly achieved thanks to the reduction in gate capacitance, which follows the reduction in the physical device dimensions. This situation is clearly reported in figure 1.6, where gate capacitance  $C_{GS}$  is plotted for each considered technology node. Of course, gate capacitance is

Figure 1.6: Gate Capacitance  $C_{GS}$  vs Overdive Voltage  $(V_{GS} - V_{TH})$  for different technology nodes

expected to be proportional to the device surface, i.e. it must be proportional to the square of the minimum channel length. This is exactly what it can be observed in figure 1.6, at least for planar technologies. With a reduction of 600% (a factor of 6) in minimum L, from 180nm to 28nm, the gate capacitance reduces by roughly a factor of 36, from 2.4fF down to 0.07fF. Even in this case 16nm FinFET technology does not follows the planar nodes trend. The 3-dimensional shaped gate, the so-called fin, introduces several parasitic capacitors above the channel, especially in the corners, that shows up more and more as the channel is forming (i.e. as the overdrive increases). This means that in strong-inversion region, when the channel is completely formed, gate capacitance of a minimum length transistor becomes even larger than a 28 nm MOS, which physical dimension are almost the double.

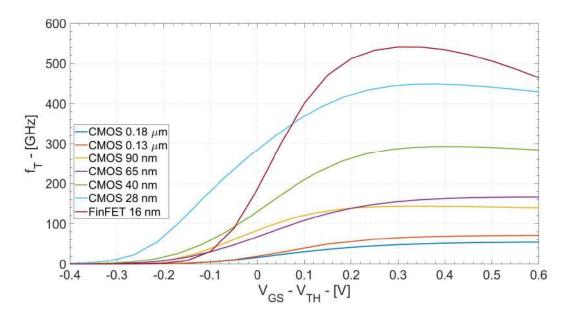

This capacitance reduction trend translates, as it can be expected, in an increase in the transistor transition frequency. This means that the smaller the devices becomes, the faster they are, which is in fact one of the main reasons of the downscaling process. As it can be noticed from figure 1.7,  $f_T$  increases from the 50GHz of a minimum 180nm transistor up to 450GHz of a 28nm MOS. This 9 times increase makes possible several RF applications, such as the ones suitable for 5G, that exploit the GHz bandwidth available in this ultra-scaled technology nodes. It is necessary to underline that, despite an increase in gate capacitance compared to less scaled nodes, 16 nm FinFET

Figure 1.7: Transistion Frequency  $f_T$  vs Overdive Voltage  $(V_{GS} - V_{TH})$  for different technology nodes

technology can easily reach 550 GHz in transition frequency at 200 mV overdrive voltage. This situation is the result of an increased transconductance, especially when the gate voltage is larger than the threshold voltage, that allows to overcome the increased gate parasitic capacitance.

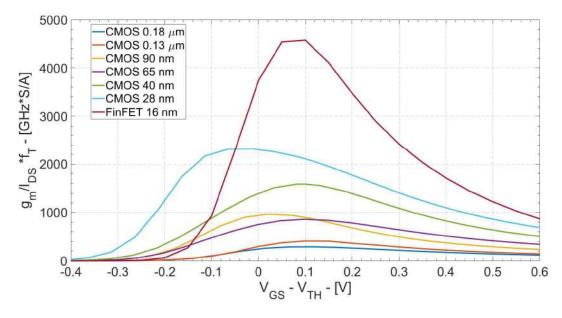

Last, it is possible to combine transistor efficiency and transition frequency

Figure 1.8: Efficiency-Transition Frequency product vs Overdive Voltage  $(V_{GS} - V_{TH})$  for different technology nodes

in order to obtain the most important Figure-of-Merit for analog designers, the efficiency-transition frequency product. Plot of this FoM vs the overdrive voltage for

each considered technology is reported in figure 1.8.

As it can be noticed, for every technology it exists a sweet spot in terms of overdrive voltage in which transistor performances (noise, bandwidth and power consumption) reach their maximum. The newer and smaller the technology node, the better are the performances. This is mainly due to the larger increase in the transition frequency, which effectively balances and overcomes the decrease in MOS efficiency. It is also possible to notice that the trend in planar technology is to move the optimal performances point to a gate voltage which is 100-200 mV below the overdrive voltage. In this region in fact, the transition frequency is starting to reach very large values and the efficiency is not yet decreased as in the strong-inversion region. Again, 16nm FinFET does not follow the common trend. This technology performances are indeed the best among the considered technology nodes, but the sweet spot is shifted to an overdrive voltage of 100mV. This situation, could be considered a disadvantage, given the low supply voltage. On the contrary, the reduced threshold voltage (100 mV lower than 28nm node) makes possible to bias transistor with a larger overdrive voltage compared to the 28 nm node, improving noise, linearity and bandwidth performances, without a significant power consumption increase.

Figure 1.9:  $I_{DS}$  vs  $V_{DS}$  for different technology nodes

#### 1.2.5 Bias Current vs Drain-Source Voltage

For what it concerns Drain-Source Voltage dependent performances, they can be reduces to the transistor Intrinsic Gain alone. This performance, as reported in equation 1.5, only depends on transistor transconductance and conductance (being this last the reciprocal of the Drain-Source resistance). In figure 1.9, the characteristic curve  $I_{DS}$  versus  $V_{DS}$  is plotted but it is not possible to recognize a clear trend.

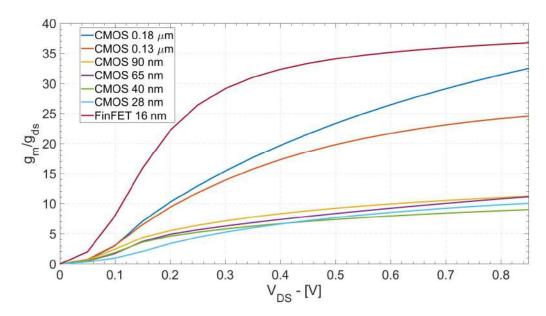

On the Other hand, in figure 1.10 transistor intrinsic gain versus drain-source

Figure 1.10: Transistor Intrinsic Gain  $(gm/g_{DS})$  vs  $V_{DS}$  for different technology nodes

Voltage is plotted. As it can be seen, the trend for planar technology is quite clear: the more transistor dimensions decrease, the more the transistor intrinsic gain decreases too. This is a direct consequence of the channel resistance reduction which follows technology downscaling. This situation translates in a loss of transistor gain of about a 60% between 180nm and 28nm CMOS. The same situation does not apply for 16nm FinFET. In this case the high-k dielectric, together with the 3-gate Fin structure, allows very high transistor output resistance, which translates in an increased intrinsic gain. In this case, for a minimum length MOS, intrinsic gain increase by more than 80% compared to the previous 28nm planar node.

#### 1.2.6 Planar vs FinFET Technology

In order to resume this chapter main topics, in this sub-section the FinFET technology most important advantages and disadvantages, compared to the 28nm planar CMOS technology, will be presented. These two technologies, in fact, are both exploited in this work for similar building blocks and, despite both nodes show downscaled technologies typical drawbacks (i.e. reduced supply voltage and low difference between threshold voltage and supply voltage, among others), they present also large differences in terms of foundamental structures one from the other, which reflect in different transistor performances.

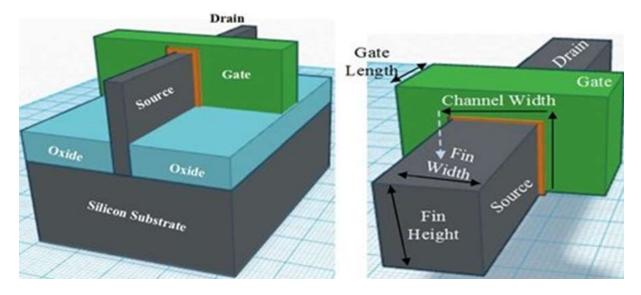

First of all, it is necessary to present the technological revolution, introduced from the 20nm node, which is named FinFET. FinFET, from Fin Field-Effect Transistor, indicates a new topology of transistors which exploit the same Field-Effect, as in the last 70 years' transistors, to modulate electrical conductivity, but in an innovative "fin" structure. The fin identifies the semiconductor channel between source and drain which is surrounded on both sides and on the top (tri-gate) or only on both sides (double-gate) by the gate contact. The Metal-Oxide-Semiconductor structure

remains almost unchanged, but the channel is wrapped inside an HKMG (High-k Metal gate) as opposed to the planar CMOS where the Oxide gate only lies on the channel top. In this way short channel effect can be strongly reduced and controlled as demonstrated by [18], even in deeply downscaled node, thanks to the gate voltage better control on the conductive charge in the semiconductor channel. In fact, it is very difficult to uniformly manage carriers along the channel in short length planar device, such as in 28nm, since the interface between gate and channel is very small. With the fin structure, this interface increases since it accounts also for the contribution of the two lateral sides of the channel surrounded by the gate contact, providing a uniform voltage all across the entire channel length. This also allows to control off-state leakage current reducing power consumption in digital cells.

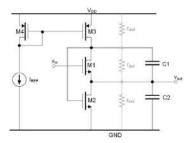

Figure 1.11: FinFET MOS Transistor device scheme

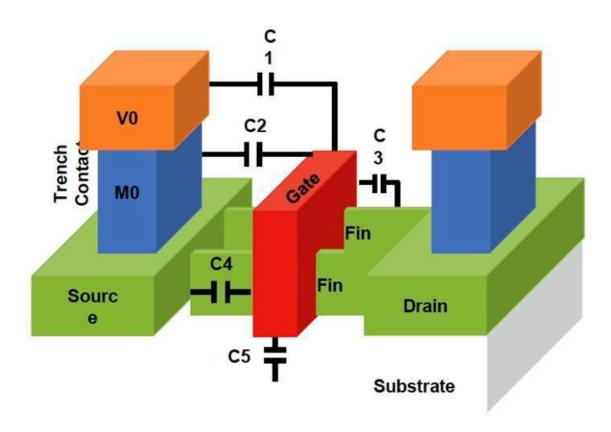

the other hand, this fin structure has several drawbacks that need to be considered. First of all, the parasitic capacitances all around the gate increase in number and value. As it is possible to understand from figure 1.6, Gate-Source Capacitance of a minimum length MOS in FinFET is comparable in size with that of a minimum length 28nm planar transistor, which surface is roughly 4 times larger. This does not impact significantly on speed performances as already stated, but this is something that must be considered when pushing devices at very high frequency (i.e. hundreds of GHz). In figure 1.12 it is possible to notice a simple scheme of the parasitic capacitances which insist on the transistor gate, and in particular the ones between the fin structure and the surrounding metal and vias. The 3-dimensional structure in fact, conversely to the planar, allows the formation of parasitic between the gate metal contact and routing and vias which are usually more distant and "higher", such as C1 and C2 in the figure.

Another drawback of this structure is the impossibility to modify transistor width and length in a continuous way. For what it concerns transistor width, it is fixed by fin dimensions and, in detail, it is calculated as the sum of the two fin heights and

Figure 1.12: FinFET MOS Transistor Gate Capacitance Scheme

the fin width, i.e. it represents the linear extend of the contact surface between the semiconductor channel and the surrounding gate oxide. It is not possible to modify none of the fin parameters and the only way to realize large transistors is to put more fin in parallel, as it is made with transistor fingers. Transistor width is in this way quantized and this means that it is possible to modify it only by large steps, in this case 48nm.

Also transistor length is quantized, but this time in a very strange way. Because of the lithographic process, in fact, only few length values are allowed for short channel transistor. In this technology these are: 16nm, 20nm, 24nm,36nm and 72nm. On the other hand, for long channel transistor, all lengths between80nm and 200nm with only 1nm step are allowed. For this reason, it is easier to design long devices, while there are few design opportunities with short devices.

Last, it is possible to resume the main FinFET drawbacks as:

- A reduced supply voltage, limited to 0.85V, which forces transistors to be biased in sub-threshold region and makes very difficult the realization of cascode topologies. (This is in common with every downscaled node).

- An increased parasitic capacitance on the gate node, which does not affect speed performances, but it must be taken into account when designing for very high

frequency applications.

- A transistor quantized length and width, which reduces design opportunity.

- Some very severe layout rules, caused by the new lithographic techniques, which increases design flow time.

For what it concerns FinFET advantages compared to the 28nm planar CMOS node, they can be resumed as:

- A larger transistor transition frequency, which translates in an increased device speed.

- A larger transistor efficiency, thanks to the larger control on the semiconductor channel which reduces leakage current.

- A reduced threshold voltage, which allows to bias MOS between weak inversion and strong inversion region, increasing noise and linearity performances.

- A larger transistor intrinsic gain, which allows better linearity performances thanks to the possibility to realize large closed-loop gain.

## Baseband Analog Filters and Variable Gain Amplifiers

#### 2.1 Analog Filters specifications for TLC applications

As already stated in the introduction, task of this thesis work is to realize ICs that could become building blocks in TLC systems suitable for the next generation standards. In detail, this work focuses on Telecommunications systems Base-Band (BB) section, neglecting Digital and RF sections.

In figure 2.1, a simplified scheme of a TLC receiver is shown, in which it is possi-

Figure 2.1: TLC Receiver basic building blocks scheme

ble to notice the most important blocks. Every TLC system, transceiver or receiver, shares, at least partially, this block structure. The BB section is usually composed by 3 main components: a Trans-Impeder Amplifier (TIA), which converts a current signal coming from the antenna, and demodulated by the mixer, into a voltage signal, an Analog Filter/Variable Gain Amplifier (VGA), which reduces the signal into the appropriate frequency range and removes interferers and noise and an Analog-to-Digital Converter (ADC), which converts the analog signal in the digital domain, in order to be properly processed by the system Digital Signals Processing (DSP) unit. This work focuses on several topologies of Analog Filters/VGA suitable for the previously mentioned TLC application.

Before we discuss each device topologies that have been developed and analyzed, it is necessary to introduce the specifications that act as guidelines for the ICs realization. First, it is good to keep in mind that 5G standard possesses only few specifications clearly defined; these help designer to have a general idea about behaviour of the final devices, but none of the competent bodies, local or international, already define in an exact way specifications for the 5G standard. 3GPP, the most important international project that deals with TLC systems standardization, only release a first part of 5G specifications, while for a second and larger part it is necessary to wait

| Specification         | Value                                     |

|-----------------------|-------------------------------------------|

| Filter Bandwidth      | From 50MHz to 100MHz                      |

| Filter Order          | $3^{rd}$ to $6^{th}$ Butterworth Low-Pass |

| Filter DC-Gain        | 0dB or 19dB or 27dB                       |

| Filter IRN            | $< 10nV/\sqrt{HZ}$                        |

| Filter IIP3 (In-Band) | > 12dBm                                   |

Table 2.1: Analog Filters Specifications

until end of 2020. That being said, it is clear that the BB performances matter is still a problem and sometimes designers tend to give more stringent specifications to these building blocks in order to be sure that they will meet final standards.

For what it concerns analog filters, the most important specifications that must be taken into account are bandwidth (associated with filter mask), noise and linearity. Power consumption is not a stringent specification, but it is a common agreement to minimize it. Since the single transmission channel width has not yet been clearly defined, designer has some freedom about the filter mask, as far as they put themselves and their specifications in a line of continuity with previous standards (4G and LTE), following their trends. For this reason, a hypothetical filter bandwidth must be at least 40MHz wide and filter order must be at least a  $2^{nd}$  order. In detail, this work has the task of explore 28nm CMOS and 16nm FinFET technology performances and push them at their limits. Therefore, Bandwidth specifications vary from 50MHz up to 100MHz according to the technology exploited for the design. The same applies to the filter order, which varies between a  $3^{rd}$  order and a  $6^{th}$  order, while the Butterworth topology has been kept the same for every designed prototype, since it is considered a standard for TLC analog filters.

For what it concerns linearity and noise performances, they must follow the main trends started in previous generations standards and their specifications will tend to be particularly stringent. In detail, noise specification was chosen as  $10nV/\sqrt{HZ}$  of Input Referred Noise (IRN), while linearity specification was chosen as 12 dBm of In-Band 3rd Order Input Intercept Point ( $IIP_3$ ).

In the case of variable gain structures, voltage gain specification follows from accurate system analysis which are specific of each application. In this case, the Variable Gain Amplifier that was designed is suitable for a 5G Full-Duplex Transceiver, which application forces 19dB DC-Gain in the main path and 27dB in the auxiliary path.

Table 2.1 resumes the main specifications exploited in each design presented in this thesis work.

#### 2.2 Analog Filters Topologies

During the years, several different circuital topologies were developed in order to meet specifications from table 2.1. Each topology of course has several advantages and drawbacks in terms of performance if compared to the others. Three topologies are worth to be mentioned: Active-RC [19]-[20]-[21]-[22], Active-gm-RC [23]-[24]-[25],

source followers [26]-[27]-[28] and gm-C [29]. While still widely used in several applications, gm-C filters seem to be less exploited compared to the other topologies, especially because, even if they achieve low noise and low power performances thanks to the open loop operation, their frequency response is usually quite inaccurate. For this reason, in this work we will focus only on Active-RC and Source Follower analog filters.

#### 2.2.1 Active-RC Analog Filters

Active filters are particular analog filters that exploit an active component, usually an amplifier or a buffer, and a feedback network, composed of passive elements such as resistor and capacitance, in order to integrate a desired transfer function which does not depends on the active element performances. Compared to other topologies, Active-RC structures allows the realization of high-gain architectures with transfer functions that usually exploit complex poles pairs. They can be easily cascaded such that they can integrate high-order transfer functions, where bandwidth and quality factor only depends on the passive element in the feedback path, as long as the amplifier bandwidth and gain are much larger than the final desired ones.

Active-RC linearity performances usually are higher compared to other topologies. In fact, in this structure, signal distortion can only occur in the active element, where the transistors' characteristic is intrinsically non-linear. But at the input of the active element, the feedback path provides a virtual ground node, where signal amplitude is ideally null, and for this reason the entire structure usually remains extremely linear. Large linearity is provided if the structure loop gain remains large, i.e. usually, in low pass filters, at low frequency. When signal frequency increases and approaches closed-loop poles frequency, signal amplitude at the virtual ground node starts to increase and distortion shows up, decreasing linearity performances near to the filter band edge.

Noise performances on the other hand are usually linked to the resistances in the feedback or at the active element input, which also are used to fix the DC-Gain. This is undoubtedly an advantage since the active element noise usually does not contribute significantly to the overall noise budget and power consumption can be reduced. Low noise performances are achieved thanks to very little resistances which on the other hand can be very difficult to be driven by the previous stage, i.e. a TIA in a receiver structure.

Moreover, in order to achieve a very accurate filter frequency response, the active element must be carefully designed. Usually the golden rule is to size the amplifier bandwidth at least a decade above the filter bandwidth.

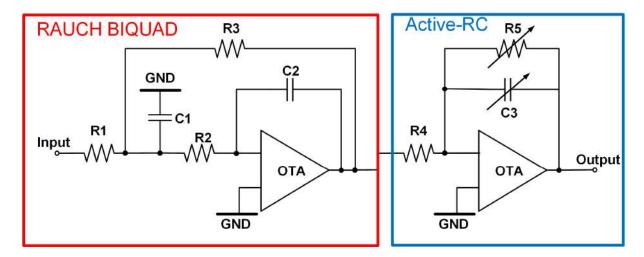

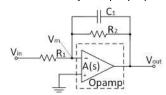

There are several structures which are commonly used that belong to the Active-RC category. On of the most exploited is the so-called Rauch topology, which single-ended scheme can be seen in figure 2.2 and will be analyzed in the following chapter. One of the main features of the Rauch cell is the possibility to integrate a complex poles pair with very low Quality factor sensitivity to finite active element DC-Gain and bandwidth as it will be illustrated in the following.

Figure 2.2: Active-RC Filter: Rauch Biquadratic cell

This work deeply analyzes 2 different Rauch based analog filters. The first is exploited in a VGA with very low noise and high linearity performances which makes it suitable in a Full-Duplex 5G transceiver. The second exploits the cascade of 3 Rauch biquadratic cells to integrate a  $6^{th}$  order filter with very low quality factor sensitivity to the amplifier finite Unity Gain Frequency. This is achieved thanks to an operational amplifier which bandwidth is maximized by an innovative compensation circuit.

#### 2.2.2 Source-Follower based Analog Filters

Another circuital topology widely exploited in the realization of IC circuit for TLC applications is the Source Follower based. This topology is based on the well-know source follower transistor structure in which the signal is applied at the transistor gate and the output signal comes from the MOS source terminal. This structure local feedback allows to realize highly linear device and the fact that only one MOSFET is involved drastically reduce noise contributions and power consumption. Of course this single transistor structure, figure 2.3 (a), can only integrate a first order transfer function. For this reason, the structure called Super-Source-Follower, presented in [30], has been developed. This Source-Follower evolution introduces a further path in feedback to the MOS in source-follower configuration (Figure 2.3 (b)). The path is composed by a common source transistor (which is dual compared to the follower MOS) and a capacitor to signal ground. This structure allows to integrate a complex poles pair and also to handle and size in a separate way noise and linearity performances by acting separately on the two MOS. Noise and power, in fact, depend on the input follower transistor, while linearity depends on the loop gain of the feedback path, which is related to the feedback MOS transconductance. On the other hand, this structure suffers from the intrinsic mismatch between the two transistors, one being an NMOS and the other being a PMOS. For this reason, a third structure [31]-[32] has been developed (Figure 2.3 (c)), called Flipped-Source-Follower. This structure allows to avoid the mismatch between the two MOS since the feedback is integrated by the help of a transistor of the same type as the input MOS, maintaining at the same

time the exact same advantages of biquadratic transfer function and performance optimization independence of the super source follower structure. The only drawback is related to the fact that the two transistors share the same bias current and for this reason, when they are biased in sub-threshold region as commonly happens in downscaled nodes, it is someway difficult to control in a separate way the transconductances of the two MOS.

Another advantage of the source-follower topology, compared to the Active-RC

Figure 2.3: Source-Follower (a), Super-Source-Follower (b) and Flipped-Source-Follower (c) Scheme

topology is the possibility to realize wide-bandwidth filters, since the transfer function of the follower, which is gm-C like, is easily tunable by increasing the input MOS transconductance. Moreover, the filter input terminal is a high impedance node (i.e. it is the source-follower gate) and for this reason the structure is easy to cascade with the previous TIA. The drawback in this case is linked to the input MOS gate node bias voltage that it is usually not at VDD/2. Moreover, the follower MOS acts as a level-shifter and for this reason input and output voltage may not be the same.

This thesis work deals with two prototype devices based on the source-follower topology. The first is realized in 28nm CMOS technology and it is the first device which exploit the Flipped-Source-Follower structure. The second is a super-source-follower in 16nm FinFET with a fully differential structure which allows better performances of power supply rejection ratio and common mode rejection ratio.

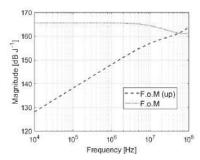

#### 2.3 Analog Filters Figure of Merit

Once the most important filter topologies, that it is possible to find in this work has been presented, it is necessary, as it has been done with transistor performances, to find a way to compare filter performances with the State-of-the-Art. Several Figure-of-Merit (FoM) were exploited during the years, which account for different analog filter parameters, with different weights. Historically, the most important Figure-of-Merit which can be found in the State-of-the-Art was introduced by [33] for Analog-to-

Digital Converters and then adapted to amplifiers and filter in [34] and it is reported in equation 2.1.

$$FoM = 10 \times \log(\frac{BW \times IMFDR_3}{Pw \times Poles})$$

(2.1)

Where:

$$IMFDR_3 = \left(\frac{IIP_3}{V_{NIN}}\right)^{4/3} \tag{2.2}$$

This FoM takes into account some of the most important analog filter performances, such as power consumption (Pw), filter mask, through the terms BW, which represents the filter bandwidth and the term Poles, which represents the transfer function number of poles, noise  $(V_{NIN})$  and linearity  $(IIP_3)$ , both included in the term  $IMFDR_3$ , which is the  $3^{rd}Order$ Inter-Modulation Spurious-Free Dynamic Range. This FoM assigns a value, expressed in dB, which is as higher as better its performances are compared to the state-of-the-art. Low noise and power consumption values tend to increase the FoM and the same applies with an high number of poles, large bandwidth and high linearity.

Thus, this Figure-of-Merit assumes as independent one from the other every performance value used for its calculation; this is not always true. Linearity performances, which are usually calculated through the  $IIP_3$  value, are, in fact, intrinsically dependent on the frequency of the input tone used for the measurement. It is sufficient to think to an Active-RC feedback structure, in which the loop-gain decreases with frequency when it approaches the closed-loop poles frequency and, because of that, signal amplitude at the amplifier input is larger. The main consequence of this situation is a distortion increase, caused by the amplifier, and, consequently, a reduction of linearity performances of the entire filter structure. Having said that, it is necessary to recognize that the FoM exploited in equation 2.1 does not take into account this performance dependence with the input frequency; this means that, according to this FoM, a device with great low-frequency linearity performances, but terrible at high frequency, will always have better figure-of-Merit compared to a filter with constant good performances through its entire pass-bandwidth. For this reason, the FoM reported in equation 2.3 was introduced firstly in [35] and then developed in [36].

$$FoM = 10 \times \log(\frac{BW \times IMFDR_3}{Pw \times Poles} \times \frac{f_{IM3Low}}{f_{cut-off}})$$

(2.3)

This new equation takes into account the distance between the frequency at which the linearity performance is measured (i.e.  $f_{IM3Low}$  which is the frequency of the lower  $3^{rd}$  order intermodulated tone in a two tones test) and the cut-off frequency ( $f_{cut-off}$ ) through their ratio. In this way it is possible to obtain a more objective

evaluation of the filter performances that allows to better analyze all these structures with frequency-dependent performances.

The FoM reported in equation 2.3 has been used to compare performances of all filter presented in this work with the State-of-the-Art. This Figure-of-Merit was first illustrated at the ICICDT 2018 conference with a presentation and a poster session, as first PHD year activity. Poster and paper are reported at the end of this work.

## **Active-RC** Analog Filters Design

Task of this chapter is to describe the 2 designs that exploit the Active-RC topology. The prototypes also shares the same 28nm CMOS technology.

First, the Rauch biquadratic cell design, which is common of both designs, will be illustrated, focusing on DC-operating point, transfer function and noise. Then, the 2 prototype peculiarity will be analyzed and measurement or simulation results will be provided. Their performances will be compared in the conclusions with the State-of-the-Art.

#### 3.1 Rauch Biquadratic Cell Design

The schematic level design of a Rauch biquadratic cell is reported in figure 2.2. It is composed by an input resistance R1, a grounded capacitor C1 and 2 different feedback paths, one composed by other 2 resistors R2 and R3 and one composed by the capacitor C2. The exploited active element is an Operational Transconductance Amplifier (OTA), with finite DC-Gain and Unity Gain Frequency, even though in this first discussion they will be assumed infinite.

#### 3.1.1 Rauch Biquadratic DC-Operating Point

The most important consideration related to the DC operating point, in each Rauch cell, is associated to the OTA input and output node voltage. In detail, these two biasing voltages needs to be the same, in order to properly connect the cell with other Rauchs (in cascade). In particular, these nodes voltage needs to be VDD/2. This constraint can be easily satisfied with almost every topology of operational amplifier. In these cases, a 2-stage Amplifier is exploited, in which the input MOS biasing gate voltage must satisfy equation 3.1.

$$V_{\rm DD} - V_{\rm IN,swing} > V_{\rm IN,CM} > V_{\rm OV} + V_{\rm TH} + V_{\rm IN,swing}$$

(3.1)

Where  $V_{IN,swing}$  is the signal swing at the OTA input and  $V_{IN,CM}$  is the common mode voltage at the same OTA input node. Since the Supply Voltage  $(V_{DD})$  in 28nm CMOS node is maximum 1.2 V and the Threshold Voltage  $(V_{TH})$  is 0.5V, very limited space is left for transistor Overdrive Voltage  $(V_{OV})$ , which is limited in this case to 0.1V. Signal swing at the OTA input is kept almost null thanks to the virtual ground principle and for these reasons the input voltage (the same as the output voltage) is equal to 0.6 V.

#### 3.1.2 Transfer Function, Noise and RC sizing

Starting with the filter specifications, it is necessary to size at least 5 different parameters in each Rauch design: R1, R2, R3, C1 and C2. First it is necessary to analyze the biquadratic transfer function reported in equation 3.2.

$$\frac{V_{\text{out}}}{V_{\text{in}}}(s) = -\frac{R3}{R1} \cdot \frac{1}{s^2 C1 C2 R2 R3 + s C2 (R2 + R3 + R2 \frac{R3}{R1}) + 1}$$

(3.2)

From this equation it is possible to isolate 3 different Biquad specifications: the cut-off frequency ( $\omega_0$ ), the DC-Gain (G) and the Quality Factor (Q), as reported in equations 3.3.

$$G = \frac{R3}{R1}; \omega_0^2 = \frac{1}{C1C2R2R3}; Q = \frac{1}{\omega_0} \cdot \frac{1}{C2(R2 + R3 + R2\frac{R3}{R1})}$$

(3.3)

In this way it is possible to size 3 parameters out of 5. A  $4^{th}$  parameter can be set as the ratio between R2 and R1 and, according to [37], this ratio can be easily set, without performance losses, as 1. The last parameter can be sized starting from noise specifications. The Input Referred Noise (IRN) can in fact be expressed as in equation 3.4.

$$IRN^{2} = 8k_{b}TR1(\frac{1+G}{G}) + (IRN_{OTA}^{2} + 8k_{b}TR2) \cdot (\frac{1+G}{G})^{2}$$

(3.4)

where  $IRN_{OTA}$  is the OTA Input Referred Noise, which is usually a specification. This allows to retrieve all 5 RC parameters starting from Biquad specifications.

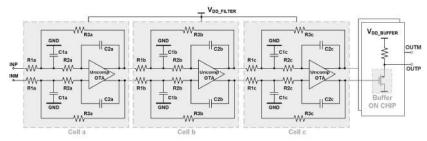

## 3.2 $6^{th}$ Order 50 MHz 18dBm- $IIP_3$ Analog Filter with 7GHz Bandwidth OTA

The first design to be presented is a  $6^{th}$  Order Low-pass Butterworth analog filter based on 3 cascaded Rauch biquadratic cells. Novelty of this prototype compared with the State-of-the-Art is the fact that it exploits wide-bandwidth OTA in order to minimize quality factor sensitivity to finite OTA DC gain and bandwidth. The OTA reach 7GHz of Unity Gain Bandwidth thanks to a novel compensation scheme which does not affect OTA bandwidth performances.

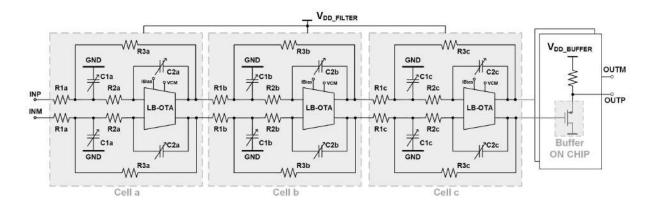

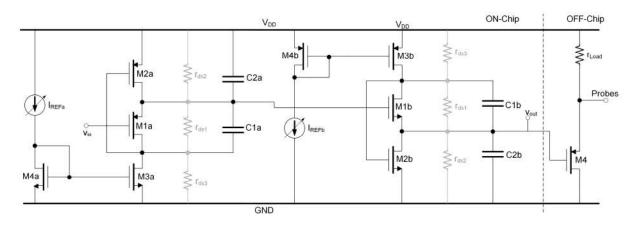

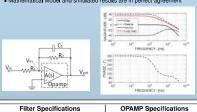

The overall filter schematic is reported in figure 3.1. Filter specification are reported in table 3.1, while RC component size, according to eq 3.3 and 3.4 are reported in table 3.2.

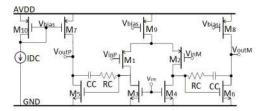

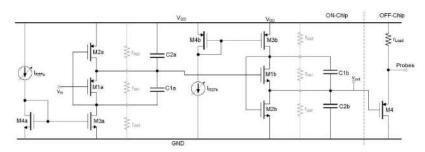

#### 3.2.1 The 7GHz OTA Design

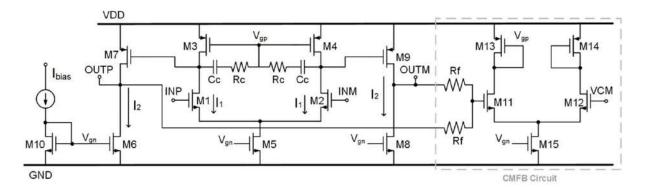

The last component to be sized for this design is the Operational Transconductance Amplifier (OTA). As a trade-off between power consumption, area occupancy, maximum OTA DC-Gain (A0) and maximum Unity Gain Bandwidth ( $\omega_{UGB}$ ), the two-stage amplifier shown in figure 3.2 was chosen. It is composed by a differential pair as input stage and a class-A output stage, without Miller or any other classical

Figure 3.1: 7 GHz OTA Active-RC filter scheme

| Specification                   | Value                              |  |

|---------------------------------|------------------------------------|--|

| Transfer Function               | $6^{th}OrderButterworthLow - Pass$ |  |

| CMOS Technology                 | 28nmBulk-CMOS                      |  |

| DC-Gain                         | 0dB                                |  |

| Poles Frequency                 | 50MHz                              |  |

| Output In-Band Integrated Noise | $280\mu V_{RMS}$                   |  |

| Band-edge IIP3                  | 15dBm                              |  |

Table 3.1: Filter Specifications

compensation scheme. This topology allows low power operation, with very low area occupancy and large maximum unity gain bandwidth (no Miller capacitor between input and output stage). Closed-loop stability is granted even with limited phase margin by the properties of the Rauch topology, which guarantees that the loop is stable as long as the OTA is stable, i.e. OTA and Loop-Gain have the same phase margin. The major drawback of this structure is the limited available DC-gain caused by the low MOST output impedance typical of the 28 nm CMOS technology.

Given this topology, the OTA DC-gain and Unity Gain Frequency can be sized starting from the associated Quality factor (Q) and Poles Frequency ( $\omega_0$ )sensitivities. The expressions of  $S_{A0}^{\omega_0}$  and  $S_{A0}^{Q}$  for an OTA finite DC-Gain are reported in equations

| Parameter       | Cell A           | Cell B           | Cell C           |

|-----------------|------------------|------------------|------------------|

| DC-Gain         | 0dB              | 0dB              | 0dB              |

| Poles Frequency | 50MHz            | 50MHz            | 50MHz            |

| Cell Q Factor   | 1.930            | 0.707            | 0.510            |

| Biquad IRN      | $21nV/\sqrt{Hz}$ | $21nV/\sqrt{Hz}$ | $21nV/\sqrt{Hz}$ |

| R1, R2, R3      | $2k\Omega$       | $2k\Omega$       | $2k\Omega$       |

| <b>C</b> 1      | 9.18pF           | 3.19pF           | 2.39pF           |

| C2              | 0.27pF           | 0.69pF           | 1.00pF           |

Table 3.2: Rauch Biquad Design Parameters

Figure 3.2: 7 GHz OTA Transistor Level Scheme

3.5.

$$S_{A0}^{\omega_0} = -\frac{G}{2A0}; S_{A0}^Q = -\frac{G}{2A0} (1 - 2Q^2 (1/G + 1/k + 1))$$

(3.5)

Where G is the Biquad DC-Gain, Q is the Quality factor and k = R2/R1 = 1. These approximations are valid for A0 » 1 and infinite OTA  $\omega_{UGB}$ . Equation 3.5 is a very powerful tool for evaluating a minimum OTA DC-gain for fixed sensitivity values, with a very simple equation. In figure 3.3,  $S_{A0}^{\omega_0}$  and  $S_{A0}^Q$  (this last one, since it depends on the Quality factor value, is reported for all the three cells according to their Q value) are plotted as a function of A0, both the exact (solid line) and approximated, according to equation 3.5 (dashed line), expressions. As it is possible to notice, for sufficiently large A0 values, there is a perfect agreement between exact and approximated curves.

Given the limited DC-Gain which can be obtained with this OTA topology in 28 nm CMOS, a value of 5% for the sensitivities to A0 was chosen, which correspond to 47 dB OTA DC-gain as depicted in figure 3.3.

A similar approach can be applied for the sensitivities to the OTA Unity Gain Bandwidth. In this case, an OTA with infinite DC-Gain and finite Unity Gain Bandwidth ( $\omega_{UGB}$ ) is considered. The approximated expressions of the sensitivities are reported in equation 3.6.

$$S_{\omega_{\text{UGB}}}^{\omega_0} = -\frac{\omega_0 Q(1 + G + G/k)}{2\omega_{\text{UGB}}}; S_{\omega_{\text{UGB}}}^Q = -\frac{\omega_0 Q(1 - \omega_{\text{UGB}}/\gamma)}{2\omega_{\text{UGB}}}$$

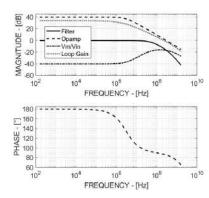

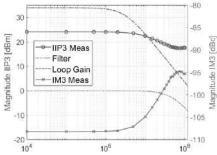

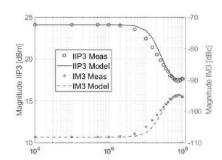

(3.6)