## UNIVERSITÀ DEGLI STUDI DI MILANO - BICOCCA Dipartimento di Scienza dei Materiali

Corso di Dottorato in Nanostrutture e Nanotecnologie Ciclo XXVIII

## CHARGE DETECTION IN SILICON DOUBLE QUANTUM DOT NANODEVICES

## Marco Lorenzo Valerio Tagliaferri

Coordinator:

Prof. Gianfranco Pacchioni

Tutor:

Prof. Marco Fanciulli

#### **Abstract**

This dissertation focuses on the characterisation of double quantum dots in silicon nano-transistors fabricated with complementary metal-oxide-semiconductor (CMOS) compliant technology.

The progressive reduction of the dimension of electronic components searched by microelectronics industry and the research on quantum dots for quantum information processing (QIP) have been regarded as independent fields. In the last years an approach combining this two aspects has gained interest: the fabrication of semiconductor nano-devices in CMOS compliant and preindustrial technology for the study of quantum mechanic effects. The core material used in this approach is silicon: it is a standard material in classical electronics and it is characterized by long coherence times. In particular double quantum dot systems are appealing for QIP because of their possible implementation in different quantum bit architectures.

This thesis reports on the work done at Laboratorio MDM-IMM-CNR of Agrate Brianza and, during a three months visit, at Hitachi Cambridge Laboratory during the three years Nanostructures and Nanotechnology PhD course of Università di Milano-Bicocca.

I first describe the formation of a double quantum dot in a single gate nano-transistor. The quantum dots are located at the corners of the channel but the presence of a single gate does not allow for controlling the system. Nevertheless, one of them is hybridized with a single donor in strong coupling with the leads. The conservation of valley parity index during tunneling influences transport processes both at first and second order. The Kondo-perturbed regime manifests in the first spin-valley shell.

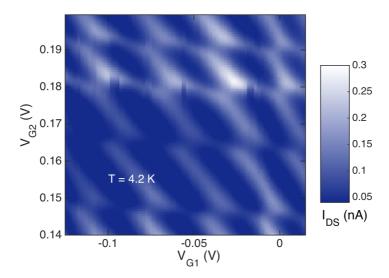

Subsequently, I report the electrical characterization of multigate T-shaped devices. Here a single electron transistor is used to charge sense nearby quantum dots. Such architecture allows for tuning the number of the quantum dots, which at low filling are disorder-assisted, and a double quantum dot can be studied both from charge sensing and single charge dynamics measurements.

I then investigate an alternative readout technique. The rf-reflectometry, by connecting a resonator to one of the gates, enables to study double quantum dots in split-gate nano-transistors, exploiting more compact and simple device architectures. In addition, the increased sensitivity with respect to standard DC measurements can be exploited to investigate the few-electron regime.

Finally, I report on the design and characterisation of a cryogenic printed circuit boards (PCBs) set for the broadband characterisation of multigate devices. One PCB hosts a custom CMOS transimpedance amplifier with selectable gain, maximum bandwidth of 250 kHz, minimum equivalent input noise of 4 pA rms. The high frequency lines are designed to ensure the transmission of ns pulses with low crosstalk up to few GHz in order to perform single charge manipulation.

#### **Abstract**

Questa tesi verte sulla caratterizzazione di doppi quantum dot in nano-transistor di silicio fabbricati con tecnologia compatibile con lo standard industriale complementary-metal-oxide-semiconductor (CMOS).

La continua miniaturizzazione dei dispositivi elettronici intrapresa dall'industria della microelettronica è rimasta a lungo slegata dalla ricerca sui quantum dot per quantum information processing (QIP). Recentemente un approccio che connette questi aspetti ha riscosso interesse: la fabbricazione con tecnologia CMOS-compatibile di dispositivi nanostrutturati o, in alcuni casi, pre-industriale per lo studio di effetti di meccanica quantistica. Il materiale cardine di questo approccio è il silicio. Infatti, da un lato è uno dei materiali comunemente usati per la realizzazione di dispositivi elettronici commerciali, dall'altro presenta lunghi tempi di coerenza, condizione favorevole per la computazione quantistica. In particolare i doppi quantum dot sono oggetto di interesse in quanto possono essere utilizzati per l'implementazione di diverse architetture di quantum bit, il che li rende estremamente versatili.

In questa tesi descriverò il lavoro svolto presso il Laboratotorio MDM-IMM-CNR e, per tre mesi, presso Hitachi Cambridge Laboratory nei tre anni del corso di Dottorato in Nanostrutture e Nanotecnologie dell'Università di Milano-Bicocca.

Inizialmente descriverò la formazione di un doppio quantum dot in un nano-transistor a singolo gate. In questo caso i quantum dot si formano agli spigoli del canale, ma la presenza di un unico gate non rende controllabile questo sistema. Nono-stante ciò, uno dei due dot è ibridizzato con un singolo donore in regime di strong coupling con i reservoir. La conservazione dell'indice di parità di valle si riflette nel trasporto al primo e second'ordine. Inoltre il regime Kondo-perturbed si manifesta nella prima completa shell spin-valle.

Successivamente, mostrerò la caratterizzazione di dispositivi a molti gate a forma di T. In questa particolare tipologia di dispositivi un transistor a singolo elettrone è usato per detettare lo stato di carica di altri quantum dot. La presenza di diversi gate permette di controllare il numero dei dot, che in regime di basso riempimento si formano grazie al disordine residuo. Doppi quantum dot possono essere studiati sia attraverso misure di charge sensing che misure di dinamica di singola carica.

Quindi sarà mostrata una tecnica di misura alternativa. La riflettometria-rf, connettendo un circuito risonante ad uno dei gate, permette di studiare doppi quantum dots sfruttando architetture piu compatte. Infatti non sono necessari elettrometri esterni ed è perciò possibile studiare la formazione di doppi quantum dot in splitgate nano-transistors. Inoltre la maggior sensitività rispetto alle misure di corrente può essere sfruttata per investigare il few-electron regime.

Da ultimo presenterò lo sviluppo e la caratterizzazione di circuiti stampati (PCB) criogenici per la caratterizzazione broadband di dispositivi a molti gate. Una PCB ospita un amplificatore a transimpedenza con guadagno variabile, massima lar-

ghezza di banda di 250 kHz e minimo rumore equivalente di 4 pA rms. Piste ad alta frequenza sono state progettate in modo da assicurare basso crosstalk fino ai GHz e la trasmissione di impulsi di pochi ns, necessari alla manipolazione di singoli portatori.

## **Contents**

| 1 | Intr | duction                                                         | 1  |

|---|------|-----------------------------------------------------------------|----|

|   | 1.1  | Context                                                         | 1  |

|   | 1.2  | This Thesis                                                     | 4  |

| 2 | Ove  | view of silicon nanoelectronics                                 | 7  |

|   | 2.1  | Introduction                                                    | 7  |

|   | 2.2  | Defining silicon quantum dots                                   | 8  |

|   | 2.3  | Single electron transport                                       | 9  |

|   | 2.4  | Kondo effect                                                    | 13 |

|   | 2.5  | SET as charge sensor                                            | 15 |

|   | 2.6  | Radio-frequency reflectometry                                   | 17 |

|   |      | 2.6.1 rf-SET                                                    | 17 |

| 3 | Cor  | er states in a single gate transistor: valley-based transport   | 25 |

|   | 3.1  | Introduction                                                    | 25 |

|   | 3.2  | Device fabrication                                              | 27 |

|   | 3.3  | Device characterisation                                         | 27 |

|   |      | 3.3.1 Quantum transport at the corners                          | 28 |

|   |      | 3.3.2 Strongly coupled quantum dot                              | 30 |

|   |      |                                                                 | 31 |

|   |      |                                                                 | 37 |

|   |      | 3.3.5 Spin-valley Kondo effect                                  | 41 |

|   |      | 3.3.6 Microwave irradiation                                     | 43 |

|   | 3.4  | Conclusions                                                     | 48 |

| 4 | Cha  | ge sensing of double quantum dots in T-shaped multigate devices | 51 |

|   | 4.1  | Introduction                                                    | 51 |

|   | 4.2  |                                                                 | 53 |

|   | 4.3  |                                                                 | 54 |

|   |      |                                                                 | 55 |

|   |      |                                                                 | 56 |

|    | 4.4    | 4.3.3 Charge dynamics in a DQD                                | 61<br>64  |

|----|--------|---------------------------------------------------------------|-----------|

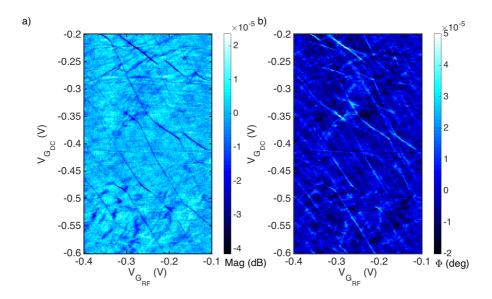

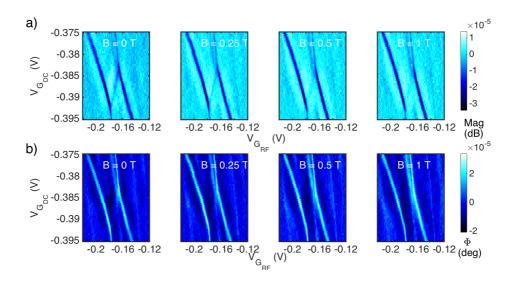

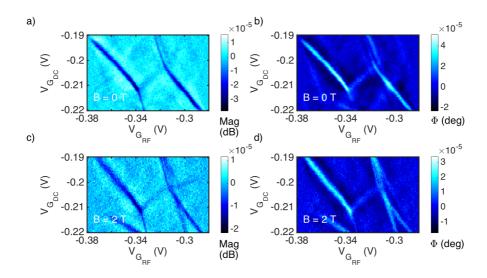

| 5  | Gate   | e-based reflectometry readout in split gate devices           | <b>67</b> |

|    | 5.1    | Introduction                                                  | 67        |

|    | 5.2    | Device fabrication                                            | 69        |

|    | 5.3    | Device characterisation                                       | 70        |

|    | 5.4    | Gate-based reflectometry of a DQD in the few-electron regime  | 75        |

|    |        | 5.4.1 DC characterisation of a DQD                            | 75        |

|    |        | 5.4.2 Rf-characterisation                                     | 77        |

|    |        | 5.4.3 Few-electron regime                                     | 78        |

|    | 5.5    | Conclusions                                                   | 81        |

| 6  | Cryo   | ogenic broadband PCBs for double quantum dot characterisation | 83        |

|    | 6.1    | Introduction                                                  | 83        |

|    | 6.2    | PCBs design and architecture                                  | 85        |

|    | 6.3    | PCBs characterisation                                         | 89        |

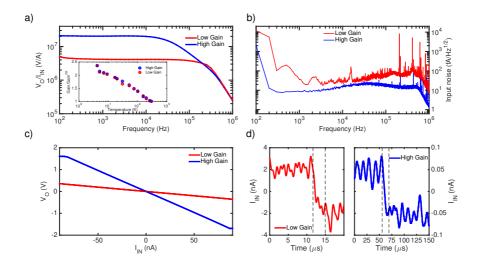

|    |        | 6.3.1 Cryogenic amplifier                                     | 89        |

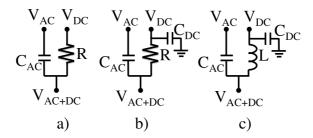

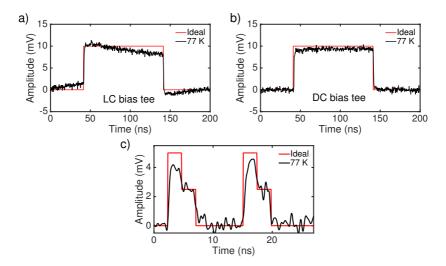

|    |        | 6.3.2 Bias tees                                               | 92        |

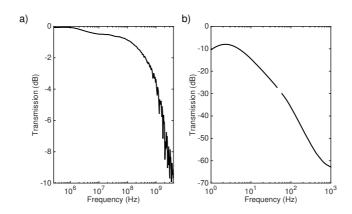

|    |        | 6.3.3 High frequency lines                                    | 94        |

|    | 6.4    | Device characterisation                                       | 97        |

|    | 6.5    | Conclusions and future perspectives                           | 98        |

| 7  | Con    | clusions                                                      | 101       |

| Ap | pend   | ix                                                            | 103       |

| Bi | bliogr | caphy                                                         | 105       |

## **Chapter 1**

## Introduction

#### 1.1 Context

Nowadays, commercial electronic devices, as laptops and smartphones, have performances which outperform by orders of magnitude, in terms of speed and computing power, the more advanced machines of only fifty years ago. In the whole history of mankind a change in technology with such big effect on everyday life has never happened so fast.

As a matter of fact, such revolution was possible because of a combination of various circumstances, which together have paved the way for the success of semiconductor technology. From the scientific point of view three discoveries are to be considered as the milestones of modern electronics: the fabrication of the first transistor at the Bells Laboratories in 1948 by Bardeen, Brattain and Shockley [1]; the realisation in the 1958-60 of the first metal-oxide-semiconductor field effect transistor (MOSFET) by Atalla and Kahng and of the first integrated circuit by Kilby [2]. From the industrial point of view different causes contributed: silicon ensures low cost processes and manufacturability and the reduction of costs by maximising the profit and improving the product, the principle of each business. The effects of these aspects are described by the so called Moore's law, empirically stated in 1965: "Every quantitative parameter [of a transistor] doubles every two years". In other words, it predicts a halving of the devices every two years with a correspondent doubling of the number of transistors in the same area and of the clock frequency. This law so predicts a decrease of the cost of the electronic devices: every two years the number of transistors built with the same amount of silicon doubles. This downscaling process proceeded along with the development of new functionalities of electronic devices.

#### Why silicon?

Historically the success of silicon as the milestone material in electronics resides on different aspects. First of all, its abundance: silicon is the second more abundant material on Earth crust, second only to oxygen. In addition, contemporaneously to the realisation of the first transistors, crystal growth and purification processes were industrially established. In the years a high degree of size control of silicon structures has been achieved thanks to the reproducibility of etching processes, even to define nanostructures. What made silicon to win, at the beginning, the competition with other semiconductors as germanium, which was used in the first transistor of 1948 [1], was the oxide (SiO<sub>2</sub>): the native oxide is extremely stable. Oxidation processes have been deeply investigated so that low charge noise can be obtained and few nm high oxides can be grown, still ensuring low leakage current. Furthermore silicon has the appealing feature to ensure an easily controlled doping, necessary process for semiconductors industry.

One of the drawbacks of silicon is the low mobility (i.e.  $10^2 \, \mathrm{cm^2 V^{-1} s^{-1}}$  in typical transistors at room temperature) with respect to other semiconductors as GaAs. However the aforementioned properties make it possible to apply large electric fields close to the transistors channel allowing for an increase of the carrier density in greater ranges than in GaAs.

Hence the large reproducibility of small sized structures was the driving force necessary for the miniaturisation of the devices dimensions, well described by the Moore's law.

Commercial devices consist of billions of transistors, in particular MOSFETs, fabricated in complementary MOS (CMOS) technology whose dimensions, nowadays, do not exceed 20 nm. The reduction of the device dimensions is expected to continue up to the 4-nm MOSFET. In fact, at this size in the channel there are less than ten silicon atoms. It is so clear that the Moore's law will not last forever: the ultimate limit of single atom electronics will be faced. It is expected that the downscaling will end in 2030. In addition at this scale other problems arise: low power consumption requirements, gate leakage and short channel effects.

#### What's next?

Nevertheless, the presence of well-established fabrication processes for silicon nanodevices opens new possibilities: the use of standard silicon transistors for the development of new functionalities. Silicon devices whose functioning relies on quantum mechanics laws (i.e. conservation laws, many body effects, etc.) are the building blocks of silicon quantum electronics [3]. Among these devices, silicon nanodevices devoted to the implementation of quantum information processing emerge.

Since the first proposal of quantum information processing in quantum dots (QDs) [4], main attention was paid to GaAs QDs [5]. The motivation relies in the intrinsic properties of such material. The growth techniques for such heterostructures are well established; quite large (as discussed in Chapter 2) quantum dots (60 nm  $\times$  60 nm) give reasonable levels spacing ( $\sim$  1 meV) resulting in fabrication processes not too demanding; phase coherence length and mean free path are longer than those of silicon (10  $\mu m$  vs 10 nm and 1  $\mu m$  vs 2 nm, respectively). Despite the early results obtained [6, 7], the coherence times have proven to be small and the architecture hardly scalable.

Silicon, on the other side, exhibits perfect properties for quantum computation based on spin degrees of freedom: the non-zero nuclear spin isotope ( $^{29}$ Si) has an abundance smaller than 5% and the most abundant isotope ( $^{28}$ Si) accounts for more than 90% of natural silicon ensuring a low hyperfine interaction; it exhibits low spin-orbit coupling, thanks to the low atomic number and monoatomic lattice, and piezoelectric coupling. Nuclear spins and phonons, in fact, cause decoherence of the electronic spins. In addition long coherence times of the order of seconds can be obtained [8, 9] thank to the capability of minimising the hyperfine coupling [10] by using substrates with a high degree of purification, in which  $^{28}$ Si represents more than 99.92 % [11]. However, to obtain a level spacing of 1 meV, because of the greater effective electron mass, smaller QDs are needed ( $^{20}$  nm  $^{20}$  nm) [12] imposing a more strict constraint on fabrication resolution and reproducibility than in GaAs QDs. However the realisation of qubits in pre-industrial silicon devices could pave the way to the realisation of really scalable qubits and quantum devices.

#### **Double quantum dots**

Different qubit architectures have been proposed and realised in semiconductor quantum dots: single donors [13], single [14] or double [6] quantum dots (DQD) where the two level system is defined exploiting nuclear spins [15], electronic spins [16], charge states [17] or orbital states [18]. In particular DQD have demonstrated to be a very versatile physical substrate in which to realise different quantum bit (qubit) architectures, thanks to the tuneability of the number of confined electrons and of exchange coupling. They have allowed for the implementation of the following architectures:

**Charge qubit** The two level system is defined by the position of an electron in the two dots.

**Singlet-triplet qubit** The logical basis consists of the two states S and T<sub>0</sub> representing two electrons in a DQD in presence of a magnetic field. Manipulation is performed using pulsed gate sequences to control the exchange and readout is performed via Pauli spin-blockade.

**Exchange-only qubit** In this architecture three electrons are trapped in a DQD. The logic basis is the tensor product of singlet and triplet states of the pair of electrons and the spin of the third electron. Manipulation is performed controlling the exchange interaction.

Such flexibility has been investigated basically in GaAs and Si/SiGe QDs, whereas CMOS compatible silicon QDs have not been yet investigated.

#### 1.2 This Thesis

This thesis reports on the characterisation of double quantum dots in silicon nano-transistors fabricated with CMOS compliant technology. In particular, different architectures for the formation of DQDs and for their charge state readout have been investigated. The thesis is thus organised as follows.

In Chapter 2 I give a brief overview of silicon quantum nanoelectronics, describing the concepts at the basis of this work of thesis.

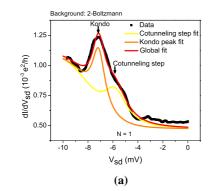

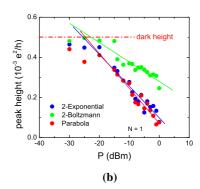

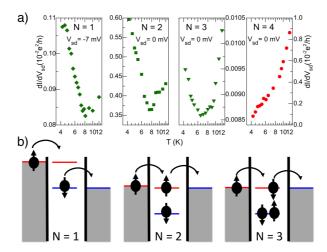

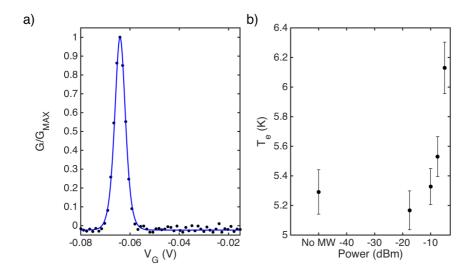

In Chapter 3 I discuss the characterisation of a single gate nano-transistor with trigate structure, fabricated with a pre-industrial process by LETI-CEA in Grenoble. In this device two quantum dots form at the topmost corners of the channel. Here, due to the lack of a second gate, I concentrate on valley-based transport through a strong coupled donor-mediated quantum dot. Asymmetries in first and second order transport features are attributed to an unintentional opposite valley polarisation of the leads in presence of valley parity index conservation during electron tunneling. The measurements have been done at the base temperature of 4.2 K, which corresponds to an electronic temperature of 5.2 K. Nonetheless, at this quite high temperature hallmarks of Kondo-perturbed regime are seen in the complete first spin-valley shell. A rigorous data analysis procedure has been established to isolate the Kondo contribution from other processes, i.e. thermally activated transport, cotunneling and photon assisted tunneling. The effectiveness of microwave suppression over the first shell is reported along with the observation of a temperature and microwave crossover, at single occupancy, between Kondo-perturbed and inelastic cotunneling regimes.

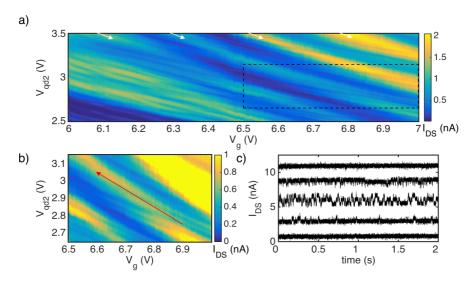

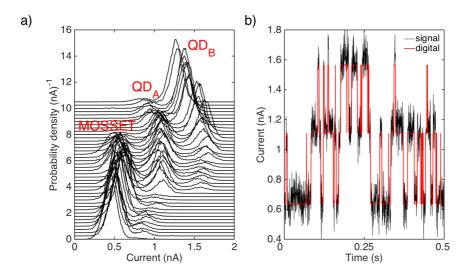

Next, in Chapter 4 I report on the electrical characterisation of multigate nanotransistors, fabricated with a CMOS compatible process in the cleanroom of Laboratorio MDM, by Giovanni Mazzeo and Davide Rotta. Such devices combine the etched-silicon technology to the multigate approach to define compact, but topologically complicated structures. The device consists of a MOS single electron transistor (MOSSET) to be used as an electrometer and three lateral gates, to electrostatically define nearby quantum dots. For the peculiar design, they are defined as T-shaped devices. Here I demonstrate that such devices can be used to define a DQD and allows for the investigation of single electron dynamics involving interdot transitions. Nevertheless, the scalable design is sensitive to charged defects,

which leads to the formation of multiple QDs under the same gate.

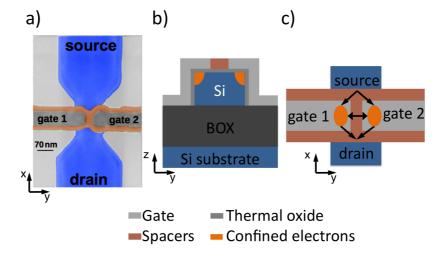

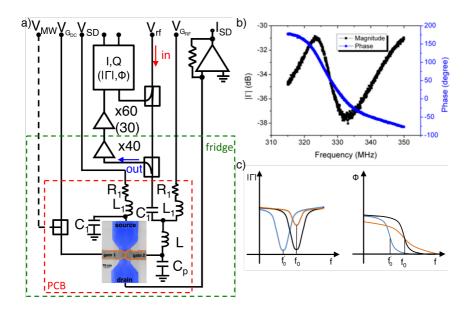

In Chapter 5 I focus on a third device structure. Split gate nano-transistors, fabricated by LETI-CEA in Grenoble, have been characterised using the rf-gate readout. Such approach has several pros with respect to standard charge sensing techniques and devices architectures. In fact, the device design is extremely compact and simple, as the double gate geometry is obtained by etching of the gate of a single gate nano-transistor. As in the device described in Chapter 3 two QDs form at the corners, but they can be independently addressed by each gate, as done in the multigate devices of Chapter 4. In addition, the alternative readout technique makes an additional electrometer worthless to study the DQD. Exploiting high frequency signals DQDs can be characterised and manipulated in two-gate devices. In addition, the high sensitivity of the rf-reflectometry allows for the detection of electrons localised in small QDs which are characterised by slow tunnel rates and/or tunnel coupled only to one reservoir: the few-electron regime can be easily investigated. Here the few-electron regime is investigated and hallmarks of singlet-triplet transitions are reported.

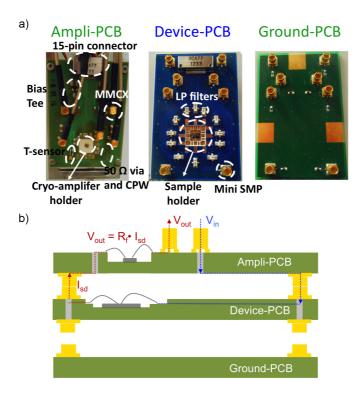

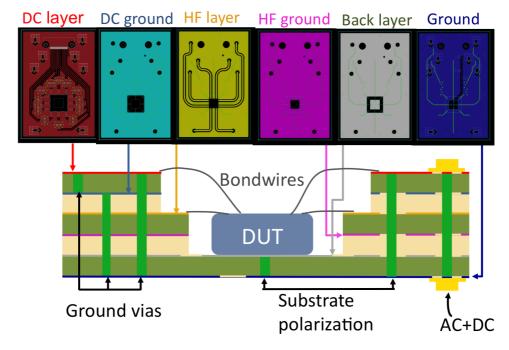

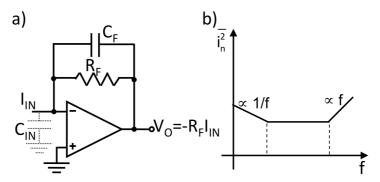

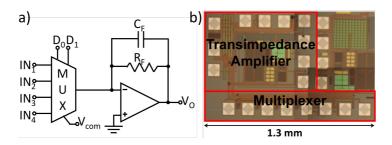

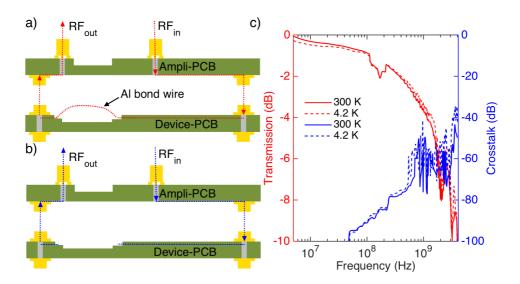

Next, in Chapter 6 I describe the design, development and characterisation of a cryogenic printed circuit boards (PCBs) set for all-electrical test of multi-gate devices. This setup improves the existing setup at Laboratorio MDM in terms of noise filtering, helium consumption, broadband of input and output signals and of low-noise amplification. In fact, it allows for the transmission of AC signals in the range 1 MHz - 1 GHz with the maximal crosstalk of -30 dB at 3 GHz; four bias tees have been designed for the transmission of ns voltage pulses; the presence of a LED and a of back gate pad enables the substrate polarisation, thus allowing the complete characterisation of single gate devices; a cryogenic four input CMOS multiplexer allows the digital selection of the device under test (DUT) among four bonded devices during the same thermal cycle; a cryogenic CMOS integrated transimpedance amplifier ensures, via a selectable gain, low noise (4 pA<sub>rms</sub>) and wide bandwidth (250 kHz) current measurements.

Finally, the main results of this work are summarised in the conclusions.

#### **Publications**

- D. Rotta, A. Vellei, M. Belli, S. Cocco, M.L.V. Tagliaferri, A. Crippa, E. Prati, M. Fanciulli, "Spin-dependent recombination and single charge dynamics in silicon nanostructrures", *The European Physics Journal Plus* 129.6: 1-4 (2014).

- A. Crippa, M. L. V. Tagliaferri, D. Rotta, M. De Michielis, G. Mazzeo, M. Fanciulli, R. Wacquez, M. Vinet, E. Prati, "Valley blockade and multielectron spin-valley Kondo effect in silicon", *Physical Review B* 92(3): 035424 (2015).

- M. L. V. Tagliaferri, A. Crippa, M. De Michielis, G. Mazzeo, M. Fanciulli, E. Prati, "A compact T-shaped nanodevice for charge sensing of a tunable double quantum dot in scalable silicon technology", *Physics Letters A* DOI:10.1016/j.physleta.2016.01.031 (2016).

- M. L. V. Tagliaferri\*, A. Crippa\*, S. Cocco, M. De Michielis, M. Fanciulli, G. Ferrari, E. Prati, "Modular printed circuit boards for broadband characterization of nanoelectronic quantum devices", (Submitted to Transactions on Instrumentation and Measurements, IEEE). (\*M.L.V.T. and A.C. equally contributed to this work)

## Chapter 2

# Overview of silicon nanoelectronics

In this chapter I provide a short overview of the relevant theories used in this dissertation. This is not intended to be an exhaustive discussion, but just an introduction to the foundations of such theories.

#### 2.1 Introduction

Silicon, in microelectronics framework, is regarded as the standard material since it has driven its development in the last 50 years. Efforts have been done, and are still done, to overcome silicon limits: new materials have been studied and developed to rule out silicon, but, as a matter of fact, many of the commercial electronic devices are silicon based. This dominant position is due to the material properties and to the well-established manufacturing techniques.

In addition, the reliable fabrication processes together with the intrinsic properties of silicon make silicon nanostructures suitable platforms to study quantum mechanics effects as the Kondo effect [19] and Landau-Zener-Stückelberg interferometry [20] or to built new quantum devices as qubits [16, 21] and logic gates [22].

Since this thesis is devoted to the investigation of silicon nanotransistors as platforms to study DQDs, this chapter concentrates only on transport of electrons in quantum dots, for more detail see, for example, Ref. 3. The chapter is organised as follows. In the first part I review the different approaches so far used to study confinement centres in silicon. Then I describe the different transport regimes of a SET so that it can be understood why nanoscaled MOSFETs behave as SETs. Next I describe the use of a SET as an electrometer in standard charge sensing scheme or by means of radio-frequency (rf) reflectometry.

#### 2.2 Defining silicon quantum dots

The confinement of electrons in silicon structures can be obtained in different ways and classifications can be made in terms of the number of directions along which electrons are confined or of the fabrication approach (bottom up vs top down). Starting with the first classification, depending on the size of the confining structure, electrons can be confined to 2, 1 or 0 dimensions. According to basic quantum mechanics [23], an electron trapped in a 3D potential well exhibits quantised energy levels where the energy spacing is:

$$\Delta_i = \frac{2\pi\hbar^2}{g_s g_v m^* L_i^2},\tag{2.1}$$

where  $g_{s(v)}$  is the spin (orbital) degeneracy,  $m^*$  the electron effective mass,  $\hbar$  the reduced Planck constant and  $L_i$  is the well width in the i direction. In order to get confinement,  $L_i$  should be comparable to the Fermi wavelength of silicon.

When the electrons are confined only in one direction, they form a two-dimensional electron gas (2DEG), which can be localised at the Si/SiO<sub>2</sub> interface in bulk silicon devices [24] or at the Si/SiGe interface in silicon heterostructures [25]. In 2DEG systems further confinement, i.e. to define QDs, is provided by several top gates, which induce soft-wall potentials along the other directions. One major advantage of this approach is that the many top gates allow for tuning the tunnel coupling with the leads or the interdot coupling in DQD systems.

Nanowires have a high aspect ratio  $(L_l \gg L_t)$  so that the energy spacing in the transverse directions  $(L_t)$  is bigger than that in the longitudinal one  $(L_l)$ . The presence of gates on the nanowire allows for defining soft-wall potentials and thus a QD by electrostatically inducing tunnel barriers. Usually in nanoscaled transistors, due to the high aspect ratio, the channel is essentially a nanowire and only the region covered by the top gate acts as active region. The uncovered portions behave as extensions of the source-drain contacts. In such devices the spacers around the gate define electrostatic tunnel barriers, or alternatively charged defects in the oxide or at the interface silicon/oxide induce the formation of QDs.

Quantum dots, or 0D structures, have nanoscaled dimensions in all the three directions so that the electrons energy is completely quantised because of the size. In the case of physically defined QDs, as silicon nanocrystals, no additional gates are needed, differently from QDs obtained from the other nanostructures by means of electrostatic confinement. Among 0D structures a special role is played by single dopants. Dopants have a radially symmetric potential, which is identical in all the directions. Since the Bohr radius of dopants in silicon is of few nm (e.g. 2.5 nm for phosphorus), only very small QDs have an energy splitting comparable to that of donors: usually QDs provide a worse localisation and the electrons wavefunctions have bigger spatial extension.

In the aforementioned list, some approaches to define QDs in silicon have emerged.

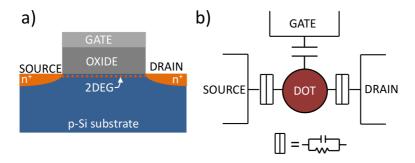

**Figure 2.1:** a) Cross section, longitudinal to transport direction, of a MOSFET. b) Schematic circuit of a SET. If tunnel barriers are defined between the reservoirs and the 2DEG in a) a SET can be obtained.

One possibility is to physically define the QDs themselves and placing them between two reservoirs and a gate [26, 27]. The other consists in further localising, by means of additional gates, electrons confined in nanowires or 2DEG. The top-down approach is the one used in etched-silicon technology: in this case a thin silicon film, usually a silicon-on-insulator (SOI) substrate, is etched to define nanowires which are subsequently gated to define FinFETs [28] or tri-gate nanotransistors [12]. This category includes even 2DEG based devices, in which QDs are completely electrostatically induced in bulk silicon by means of nanosized gates [24]. The bottom-up approach, instead, includes self assembled nanocrystals [26], chemical vapour deposition (CVD) grown nanowires [29] and STM-placed single dopants [30]. Up to date the scalability issue for device grown by bottom-up approach is still a problem, whereas the top-down approach is currently used in CMOS technology.

#### 2.3 Single electron transport

After the introduction of the confining structures, I now concentrate on how they can be used to build single electron devices. The planar MOSFET can be used as a reference to introduce the concept of single electron transistors. In the former, referring to the p-MOSFET shown in Figure 2.1a, two heavily doped regions (source and drain) act as electronic reservoirs; the gate covering the channel connecting the reservoirs is used to accumulate electrons at the silicon/oxide interface, so that a current controlled by the voltage difference between the reservoirs can flow.

When a confining centre is placed in the channel, from now on I will assume that it is a QD as shown in Figure 2.1b, the device can act as a SET. Different energy scales rule the behaviour of such a device: external ones, like the temperature T

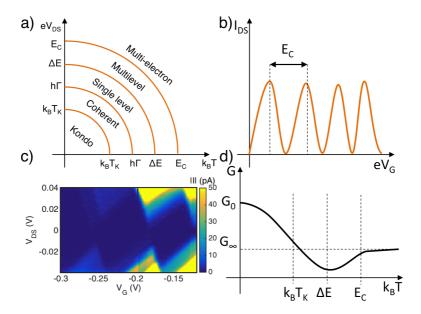

**Figure 2.2:** a) Different transport regimes in a three terminal device. Adapted from Ref. 3. In b) and c) Coulomb blockade regime is shown at small and large bias. d) Overall conductance temperature dependence in the middle of a Coulomb blocked region.  $G_0$  and  $G_{\infty}$  are the quantum of conductance and the conductance in the multi-electron regime.

and the bias voltage  $V_{DS}$ , as well as internal ones, like the charging energy  $E_C$ , the tunnel coupling or level broadening  $\Gamma$ , the level spacing  $\Delta E$  and the Kondo temperature  $T_K$ . Depending on the dominant energy scale, different regimes of QD based transistors are defined, as shown in Figure 2.2a.

When the bias  $eV_{DS}$  and the thermal energy  $k_BT$  (where e is the electron charge and  $k_B$  is the Boltzmann constant) are the leading terms, all the effects involving single electrons can be disregarded. In this limit many electrons contribute to the rising of a current and nanoscaled MOS transistors behave as standard MOS-FETs [31]. In this regime the conductance is given by the sum of the conductance through the two reservoir barriers [32]:

$$G_{\infty}^{-1} = G_L^{-1} + G_R^{-1} \tag{2.2}$$

or alternatively [33]:

$$G_{\infty} = e^2 \rho \frac{\Gamma_{\rm S} \Gamma_{\rm D}}{\Gamma_{\rm S} + \Gamma_{\rm D}},\tag{2.3}$$

where  $\rho$  is the density of states,  $\Gamma_S$  ( $\Gamma_D$ ) is the source (drain) barrier tunnel rate and therefore the level broadening is  $\Gamma = \Gamma_S + \Gamma_D$ .

When the charging energy  $E_C$  is grater than both the thermal energy and the bias, the sequential transport can take place  $(k_BT, eV_{DS} \ll E_C)$ . Let's start with

transport at small bias so that  $V_{DS} \simeq 0$ . Assuming that the capacitance of the dot does not depend on the number of confined electrons the energy required to add an extra electron to the dot (i.e. the charging energy) is  $e^2/C$ . In addition if the tunnel barriers are sufficiently opaque the transport reflects the discretisation of charge: transport takes place only when the electrochemical potential  $\mu$  of the dot (i.e. the energy needed to add an electron) is aligned to the reservoirs potentials, provided that the energy separation between  $\mu(N)$  and  $\mu(N+1)$  is the charging energy. The requirement on the barrier opacity is a direct consequence of the Heisenberg uncertainty principle. To have an energy uncertainty smaller than  $E_C$  itself, assuming a tunneling time RC (see Figure 2.1b), the tunnel resistance should be greater than  $h/e^2$ . Otherwise, the uncertainty would be so big to hide the discretisation of the electrochemical potential. In this regime the transistor is a SET in the Coulomb blockade regime.

As a result the  $I_{DS}$  -  $V_G$  traces of a SET show a periodic alternation of peaks of current and 'valleys' of zero current, as shown in Figure 2.2b. The former are spaced by the charging energy, are associated with the sequential electron tunneling and correspond to charge degeneracy conditions (i.e. the number of confined electrons oscillates between N and N+1), whereas the latter represent the conditions of well-defined charge states. When the bias  $V_{DS}$  is varied the current maps show a peculiar pattern: the Coulomb diamonds. Rhombus regions of blocked current correspond to the conditions in which the QD has a well defined number of confined electrons and the edges correspond to the alignment of the QD electrochemical potential with the source or drain chemical potential [31]. The sequential transport regime is further classified as follows:

Multilevel regime In this regime the energy spacing can be disregarded since  $\Delta E \ll k_{\rm B}T, {\rm eV_{DS}}$ . In such regime, therefore, the dot is defined as metallic. The current can be obtained from rate equations [34] and it reads:

$$I_{DS} = e^{\frac{\left(\sum_{i=1}^{n} \Gamma_{in}^{i}\right) \Gamma_{out}^{1}}{\sum_{i=1}^{n} \Gamma_{in}^{i} + \Gamma_{out}^{1}}},$$

(2.4)

where the subscripts label the direction of transport and i the levels. It is clear that the current depends on the outgoing rate of only the ground state: electrons can enter whichever state, ground or excited, but the relaxation is generally faster than tunneling out from excited levels so that transport in this regime is not coherent [3]. The lineshape of conductance peaks is [33]:

$$G = \frac{1}{2} \cosh^{-2} \left( \frac{e\alpha (\mathbf{V}_{G} - \mathbf{V}_{0})}{2.5k_{B}T} \right) G_{\infty}, \tag{2.5}$$

where  $V_0$  is the peak position and  $\alpha$  is the conversion factor between gate voltage and energy, or lever arm and is equal to  $C_G/C$ . Notably the maximum of the peak is independent from temperature and corresponds to one

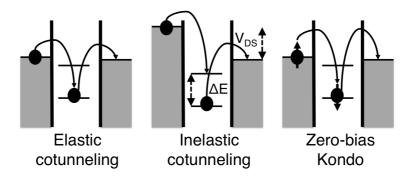

**Figure 2.3:** Different second-order processes. From left to right: elastic cotunneling, inelastic cotunneling and Kondo type coherent spin-flip cotunneling. As two electrons are involved two possible virtual states are identified: the dot is "empty" or double occupied.

half of  $G_{\infty}$ , because of the correlation between tunneling events. The full width at half maximum (FWHM) of the peak is linear with the temperature: FWHM  $\approx 4.35~k_{B}T$ .

Single level regime When the level spacing is not negligible ( $\Delta E > \mathrm{eV_{DS}}, k_\mathrm{B}T$ ) transport takes place through only one level. As a consequence the assumption that the peak spacing corresponds to the charging energy is not true anymore: this spacing, now, reflects the energy spectrum and the levels degeneracies. The addition energy is now  $E_C + \Delta E$ . The conductance peaks lineshape reads [35]:

$$G = \frac{1}{\rho 4k_{\rm B}T} \cosh^{-2} \left( \frac{\mathrm{e}\alpha (\mathbf{V}_{\rm G} - \mathbf{V}_{\rm 0})}{2k_{\rm B}T} \right) G_{\infty}. \tag{2.6}$$

In this regime therefore the peak height linearly increases when decreasing the temperature and the FWHM  $\approx 3.5~k_BT$ . Furthermore this regime is a crossover for coherent tunneling and when the QD is in strong coupling regime with the leads second order transport becomes visible in the blocked regions. In such processes transport happens via virtual states, involving a pair of electrons. Two kinds of cotunneling processes are identified: elastic and inelastic. In the former case the initial and final states of the quantum dot are the same (see Figure 2.3), so these processes give rise to a uniform extra current inside the Coulomb diamonds. In the second case the final and initial states differ at least by the level spacing between two consecutive states. Therefore inelastic cotunneling gives rise to a current only when level spacing is equal to, or smaller than, the bias window: lines of current are thus visible in the blocked regions [36].

Coherent regime Till now the Kondo binding energy  $(k_BT_K)$  and the level broad-

ening  $(\hbar\Gamma)$  have been the smallest energy scales, so that they have been disregarded. In the limit  $T_K \ll k_{\rm B}T, {\rm eV_{DS}} \ll \hbar\Gamma$  the system is in the coherent regime and the conductance reads [33, 37, 38]:

$$G = g \frac{\mathrm{e}^2}{h} \frac{\hbar^2 \Gamma_{\mathrm{S}} \Gamma_{\mathrm{D}}}{[\mathrm{e}\alpha (\mathbf{V}_{\mathrm{G}} - \mathbf{V}_{\mathrm{0}})]^2 + (\hbar \Gamma/2)^2},\tag{2.7}$$

where g is the level degeneracy. In the limit of symmetric barriers (i.e.  $\Gamma_{\rm S} = \Gamma_{\rm D}$ ) the FWHM is limited by  $\Gamma$  and the maximum of the peak is  $g{\rm e}^2/h$ , which yields the quantum limit  $2{\rm e}^2/h$  for a spin degenerate level.

**Kondo regime** The last regime, which will be described in more detail in the next section, emerges when the so-called Kondo temperature is comparable to T. This regime is linked to coherent second order processes which lead to an increase of the conductance in the blocked region when decreasing the temperature, as shown in Figure 2.2d. In particular when  $T \ll T_K$ , for a spin degenerate level, the conductance reaches the quantum limit  $2e^2/h$  [39].

#### 2.4 Kondo effect

Firstly developed to describe electron scattering in metals in presence of magnetic impurities, the Kondo model can be used to describe coherent spin-flip cotunneling in SET. The only difference between magnetic impurities in metals and QDs with spin degenerate levels at odd occupation is the manifestation of the Kondo physics: in the former case it leads to an increase of the resistance by lowering the temperature, in the latter one it causes an increase of the conductance. As in the Kondo regime a many-body singlet is formed between the localised electron spin and the spins of close conduction electrons, the scattering consists of flips of the localised spin, being the impurity or QD state spin degenerate (see Figure 2.3c). Such process leads to an increase of the scattering, which in bulk metals corresponds to an increase of the resistance. In three terminal devices based on QDs, being the current due to scattering processes, this state opens an additional transport channel for electrons, thus an increase of the conductance.

Since the theoretical scenario is the same, I concentrate on the QDs physics. The problem can be described in terms of a single level Anderson hamiltonian [40], where the leads are reservoirs of free electrons with continuous energy spectrum and the dot has a single spin degenerate level  $\epsilon_0$  and the condition  $\epsilon_0 < \mu < U + \epsilon_0$  holds, being  $\mu$  the Fermi level of the reservoirs at zero bias and U the addition en-

ergy:

$$H = H_{leads} + H_{dot} + H_T, (2.8)$$

$$H_{leads} = \sum_{\alpha = S.D} \sum_{k,\sigma} \epsilon_{k,\sigma}^{\alpha} l_{k,\sigma}^{\dagger \alpha} l_{k,\sigma}^{\alpha}, \tag{2.9}$$

$$H_{dot} = \sum_{\sigma} \epsilon_0 d_{\sigma}^{\dagger} d_{\sigma} + U n_{\sigma} n_{\bar{\sigma}}, \qquad (2.10)$$

$$H_T = \sum_{\alpha = S.D} \sum_{k,\sigma} (V_k^{\alpha} l_{k,\sigma}^{\dagger \alpha} d_{\sigma} + H.c.), \qquad (2.11)$$

where  $\alpha$  labels the two leads, k represent the leads levels and  $\sigma$  the spin state. The operators  $l^{\dagger}, l$  create and annihilate noninteracting fermions in the leads,  $\epsilon_0$  is the single-particle energy level of the QD and  $d^{\dagger}, d$  are the creation and annihilation operators of this state. U is the Coulomb repulsion,  $n = d^{\dagger}d$  is the number operator and  $V_k^{\alpha}$  are the dot-lead coupling terms.

From  $H_T$  the tunneling rate  $\Gamma_{S(D)}$  can be obtained as:

$$\Gamma_{S(D)} = 2\pi \sum_{k} |V_k^{S(D)}|^2 \delta(\epsilon - \epsilon_k). \tag{2.12}$$

It is clear that the stronger the coupling between the dot and the leads, the higher the tunneling rates. Performing a Schrieffer-Wolff transformation [41] the Kondo hamiltonian is obtained [42]:

$$H_K = H_{leads} + J(S_1 \cdot S), \tag{2.13}$$

$$J = \Gamma\left(\frac{1}{\epsilon_0} - \frac{1}{U + \epsilon_0}\right),\tag{2.14}$$

where S is the spin of the electron in the dot,  $S_1$  is a single-particle spin- $\frac{1}{2}$  operator representing the manybody spin of the leads electrons [32] and J is the exchange coupling, provided that  $\Gamma_S = \Gamma_D$ . The ground state of such hamiltonian is therefore a singlet, separated from the triplet state by J. As a consequence, a resonance appears in the QD DOS, pinned at the Fermi level of the reservoirs, detectable in conductance measurements. Usually this resonance in the DOS emerges in conductance plots only at zero bias, since at larger bias dissipative transport acts as a source of decoherence [43]. The Kondo temperature gives the binding energy of such ground state and reads [44]:

$$T_K = \sqrt{\epsilon_0(U + \epsilon_0)} \exp(-1/2\nu J), \qquad (2.15)$$

where  $\nu$  is the density of states (DOS) of the leads. From Equation 2.15 it is evident that the higher the exchange coupling, the bigger the Kondo temperature. In addition, given that in three terminal devices  $\epsilon_0$  is controlled by the gate, the Kondo

temperature can be tuned by the gate voltage: the higher Kondo temperatures are reached near the charge degeneracy points, whereas between two Coulomb peaks the temperature is minimal [45].

The temperature dependence of the zero bias Kondo resonance is non trivial. For  $T \geq T_K$  a logarithmic dependence is predicted, whereas for  $T \ll T_K$  a saturation at the quantum limit  $2e^2/h$  is expected [32]. Nonetheless, this scaling is well described by the semiempirical law [46]:

$$G(T) = G_0 \left(\frac{T_{\rm K}^{'2}}{T^2 + T_{\rm K}^{'2}}\right)^s \tag{2.16}$$

where  $T_{\rm K}^{'2}=T_{\rm K}/\sqrt{2^{1/s}-1},\ s$  is generally 0.22 [35] and  $G_0$  is the saturation value.

From the discussion developed so far it emerges that the Kondo effect appears only for odd electron occupations. However, it has been demonstrated that the Kondo physics is richer. In particular a Kondo resonance develops whenever a nearly-degenerate condition is reached: singlet-triplet Kondo [47] and higher symmetry [48] Kondo effect have been reported. In particular, higher symmetries as SU(4) can be obtained exploiting an additional pseudo-spin: magnetic field induced orbital degeneracy [49], valley index in carbon nanotubes [50, 51], in silicon [19, 52] or charge degeneracy in GaAs DQDs [35]. In such systems the aforementioned theory has to be adapted starting from a two-level Anderson hamiltonian; for more details see Refs. 44, 48, 53, 54. The Kondo temperature in SU(4) symmetry results higher than that of SU(2) since:

$$T_K^{SU(4)} = \sqrt{\epsilon_0(U + \epsilon_0)} \exp(-1/4\nu J)$$

(2.17)

### 2.5 SET as charge sensor

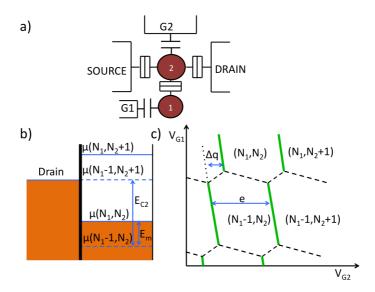

From the previous discussion it is clear that a SET can be used to extract valuable information on donors and QDs. It has been reported [55] that a SET is sensitive to the presence of nearby charges, as traps or other confining centres. Because of a capacitive coupling between these centres and the SET, a change in the number of electrons in the nearby localisation centres corresponds to a shift in the SET electrochemical potential which can alter the manifestation of the Coulomb diamonds [56]. This shift can be correlated to the SET sensitivity to nearby charges: the addition of an extra electron to the SET, in the metallic regime, corresponds to the charging energy, so that shifts smaller than  $E_C$  correspond to variations of fractions of an electron charge.

This high sensitivity can be exploited to study the charge and the spin configurations of nearby quantum dots, by means of spin to charge conversions. Such goals

**Figure 2.4:** a) Schematic circuit of a QD (1) tunnel coupled to a SET (2). For the sake of clarity, the cross-capacitances have been neglected. b) Schematic energy diagram: until the unconnected dot is "empty" current flows through the SET, but as soon as it charges the current is blocked. c) Schematic current plot with the usual honeycomb pattern associated with a DQD system.

have been obtained in GaAs heterostructures in the early 2000s [7, 57, 58] and more recently in Si/SiGe heterostructures [59, 60]. However, in heterostructures usually a quantum point contact (QPC) is used instead of a SET, as a QPC, being a constriction through which charges flow, can be controlled by only one additional gate. The use of a SET as a charge sensor in silicon MOS framework leads to complicated devices with a high number of gates [14, 24] which limit the scalability of qubits architectures. In the ideal case of a SET tunnel coupled to a nearby QD only two gates are required: one to control the SET and one for the QD (see Figure 2.4a). Due to the capacitive coupling between the two dots, the charging of the unconnected QD (1 in Figure 2.4) causes a shift  $E_m$  in the SET potential. Such shift of the potential translates in a shift of the current lines associated to the SET, as depicted in Figure 2.4c. It is common to label the SET line spacing as e, since one electron is added to the SET, thus  $E_m$  is labeled  $\Delta q$ , since it represents the charge induced in the SET by the other QD (see Figure 2.4c) [61, 62]. Their ratio  $\Delta q/e$  is the charge transfer signal (CTS) which expresses the SET sensitivity. Another fundamental parameter is the difference in the current levels between the two charge configurations (with or without an extra electron) of the unconnected dot: when the current line broadening is smaller that  $E_m$  the difference in current is maximised and the readout has a higher fidelity.

#### 2.6 Radio-frequency reflectometry

From the previous discussion it was clear that the SETs, thanks to their sensitivity to fractions of charge, can be successfully used as charge sensors and single shot measurements [63], as well as single qubit operations [16], can be performed. However a SET suffers at low frequency of limited sensitivity and at high frequency of limited bandwidth. Such limitations restrict the possible use of SETs as charge sensors only in a narrow frequency range, usually up to tens of kHz.

The charge sensitivity is proportional to the square root of the current noise spectral density [64], which has two major contributions. As depicted in Figure 2.1b, the QD of a SET is connected by two tunnel barriers to the reservoirs. Therefore, such barriers, modelled as a resistance and a capacitance in parallel, are affected by thermal or Johnson noise. The second contribution is the shot noise associated with the Poissonian nature of the tunnelling through such barriers. In both cases the noise contribution is "white", so they are dominant at very low frequencies. However to explain the discrepancy between the theoretical sensitivity limited only by these sources of noise [65, 66] and the experimental ones [67], external factors have to be considered. Two external sources of noise play a fundamental role: the amplifier stages and the flicker, or 1/f, noise. For the former case the key parameter is the noise temperature  $T_N$  [68] of each amplifier. Since in cascade amplifiers the noise of the first stage is amplified as well as the signal by the subsequent amplifiers, ideally the  $T_N$  of the first amplifier should be as low as possible. The flicker noise originates from the time-dependent occupation of charged defects and causes a fluctuating charge offset.

In terms of speed, the bandwidth of a SET is limited by the  $RC_{IN}$  constant of the tunnel barrier and the parasitic input capacitance of the amplifier, which consists mainly of the cabling capacitance and can easily reach hundreds of picofarad. A rough estimate can be done substituting the typical values of the tunnel resistance  $(100 \, k\Omega)$  and of the input capacitance  $(0.1 \, nF)$  which yield a bandwidth of 15 kHz. A widely adopted solution to increase the operating speed of a SET (bandwidth up to  $100 \, \text{MHz}$  [69]) and to ensure a better sensitivity [68] consists in embedding it in a resonant circuit, usually a LC, to build up a rf-SET as proposed in Ref. 69.

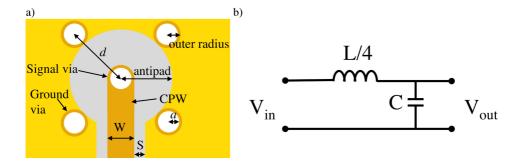

#### 2.6.1 rf-SET

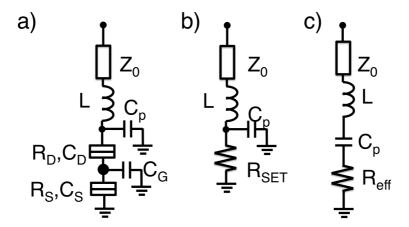

In a rf-SET the readout of the charge state is performed by monitoring the damping of the high frequency signal. The resonant circuit usually consists of a surface mount (SMD) inductor and the parasitic capacitance to ground, as shown in Figure 2.5a. Since usually the order of magnitude of such capacitance is 0.1 pF, to have a resonance in the frequency range of 0.1 - 2 GHz the inductance (L) should be of the order of hundreds of nH. Such range of frequency is fixed by the high frequency components (such as amplifiers, directional couplers, splitters, attenu-

**Figure 2.5:** a) Schematic circuit of a SET embedded in a resonant tank circuit, constituted of a SMD inductor and the parasitic capacitance to ground. b) In the linear approximation the SET can be modelled as a real impedance, namely  $R_{\rm SET}$ . c) Near resonance, the circuit in b) can be replaced by a RLC series.

ators and demodulators), forming the 50  $\Omega$  line connecting the resonator to room temperature instruments. The tank circuit thus connects the 50  $\Omega$  line to the high impedance SET and, near the resonance frequency, it acts as an impedance transformer, transforming the SET impedance to a value close to 50  $\Omega$ . Two different implementations of a rf-SET are possible: reflection or transmission configuration. In the latter case the resonator is connected to the drain and the rf-signal is collected from the source [70]; in the former the signal reflected from a combination of impedance transformer and the SET is collected, therefore a directional coupler is needed [69]. In the following the reflection configuration will be described, as it is the base of the gate readout technique used in Chapter 5.

The high frequency operation has, in addition, two major advantages. At radio frequencies the 1/f noise is negligible [71]. Secondly, the use of 50  $\Omega$  high frequency amplifiers makes the cabling capacitance unimportant. In fact, in a 50  $\Omega$  line the impedance of coaxial cables ( $Z_0 = 50~\Omega$ ) is equal to that of the amplifier, so that the combined impedance is still 50  $\Omega$ .

As clear from the discussion about the principles undergoing the working of a SET, such device is strongly non-linear. However, if the SET capacitance is much smaller than the shunting capacitance  $C_p$  of the transformer, the SET can be assumed to have a linear, real impedance [71, 72]. Typically,  $C \le 1$  fF and  $C_p \ge 100$  fF, so that the global circuit including the resonator and the SET can be modelled by the simpler RLC circuit depicted in Figure 2.5b. The total impedance of such

circuit is:

$$Z = i\omega L + \left(R_{\text{SET}}^{-1} + \left(\frac{1}{i\omega C_{\text{p}}}\right)^{-1}\right)^{-1}.$$

(2.18)

By definition, at the resonance frequency  $(\omega_0)$  the reactance is zero so it can be easily obtained:

$$\omega_0 = \sqrt{\frac{1}{LC_p} \left( 1 - \frac{L}{R_{\text{SET}}^2 C_p} \right)} \approx \sqrt{\frac{1}{LC_p}}, \tag{2.19}$$

where the approximation holds since for the typical values of L,  $C_{\rm p}$  and  $R_{\rm SET}$   $L/(R_{\rm SET}^2C_{\rm p})\ll 1$ . When  $\omega R_{\rm SET}C_{\rm p}\gg 1$ , as in typical measurement conditions, the circuit in Figure 2.5b can be replaced with a RLC circuit [71], as the one depicted in Figure 2.5c. Thus, now, Equation 2.18 becomes:

$$Z = R_{\text{eff}} + i\omega L + \frac{1}{i\omega C_{\text{p}}},\tag{2.20}$$

where

$$R_{\rm eff} = \frac{L}{R_{\rm SET}C_{\rm p}}. (2.21)$$

Near resonance Equation 2.20 reads:

$$Z = R_{\text{eff}} + 2i\sqrt{\frac{L}{C_{\text{p}}}} \frac{\omega - \omega_0}{\omega_0}.$$

(2.22)

It is therefore clear that the tank circuit acts effectively as an impedance transformer. When measuring a rf-SET in reflection configuration the key parameter is the coefficient of reflection,  $\Gamma$  (which is not to be confused with the tunneling rates  $\Gamma$  used in the previous sections), which is a function of the impedance mismatch between the 50  $\Omega$  line ( $Z_0$ ) and the impedance of the SET:

$$\Gamma = \frac{Z - Z_0}{Z + Z_0}.\tag{2.23}$$

Taking into account that Z is a function of frequency, Equation 2.23 shows that  $|\Gamma|$  has a minimum at resonance, where the impedance transformer is effective, indicating that a fraction of the incident power is dissipated at the SET. When the matching condition  $R_{\rm eff}=Z_0$  is fulfilled, at resonance  $|\Gamma|=0$ , the power is completely dissipated and reflection does not take place. Away from resonance, in the ideal case,  $|\Gamma|$  tends to 1, indicating that all the signal is reflected. When the matching condition is not fulfilled, the SET can be undercoupled ( $R_{\rm eff}>Z_0$ ) or overcoupled ( $R_{\rm eff}< Z_0$ ) depending on the resonance bandwidth limiting factor. In the former case the limit is caused by the SET and LC circuit, whereas in the latter

it resides in  $Z_0$  [71]. By measuring the phase and amplitude (or the power) of the reflected signal it is possible to monitor  $\Gamma$ , in fact, since  $V_r = \Gamma V_{in}$ ,  $P_r = |\Gamma|^2 P_{in}$  and  $\theta = \tan^{-1} \frac{\operatorname{Im}(\Gamma)}{\operatorname{Re}(\Gamma)}$ .

Another important parameter is the quality factor Q, which is the ratio between the energy stored in the system and the energy lost per cycle. The unloaded quality factor of the SET is  $Q_{\rm SET}=R_{\rm SET}/\sqrt{L/C}$  and the external quality factor is  $Q_e=\sqrt{L/C}/Z_0$ . The total (loaded) quality factor for the circuit in Figure 2.5c is the sum of the two contributions:

$$Q^{-1} = Q_e^{-1} + Q_{\text{SET}}^{-1} \tag{2.24}$$

At the matching condition it holds that  $Q = Q_{\rm SET}/2 = Q_e/2$ . The total quality factor sets the bandwidth by the relation:

$$Q = \omega_0 / B, \tag{2.25}$$

where B is the bandwidth of the rf-SET.

In the model developed so far, any change in the reflected signal is caused by a variation of  $R_{\rm SET}$ : the other parameters appearing in the various equations are constant, unless there are changes in the measurements setup. Moreover, changes in  $R_{\rm SET}$  have limited effects: the resonance frequency will remain the same and the global effect will be a variation in the damping of the resonance. However, effects related to variation of the capacitance of the QD have been reported in literature [68, 73]

Therefore the model has to go beyond the linear approximation. A simple improvement consists in replacing  $C_p$  with the parallel of such parasitic capacitance and an effective capacitance  $C_{\rm eff}$  describing the SET [74]. As a results, all the previous formulae still hold, with the difference that  $C_p$  has to be substituted by  $C_{\rm p} + C_{\rm eff}$ . Looking at Equation 2.22, it turns out that now even the capacitance has an effect on the reflected signal, more pronounced than a pure resistive variation. A change in the SET effective capacitance translates in a change in both the amplitude and phase of the reflected signal, since both the resistance and reactance are function of such capacitance. As a results a variation of  $C_{\rm eff}$  causes a change in the frequency of resonance. In addition, this additional capacitance can be rewritten, stressing its origin, as the sum of a geometrical capacitance, which is the linear part of the capacitance and accounts for the capacitive coupling of the QD with the electrodes, and of a quantum capacitance, which is non-linear and accounts for the quantum mechanics laws [75]. So  $C_{\rm eff} = C_{\rm geom} + C_{\rm Q}$ , where the first term gives only a constant additional term to the parasitic capacitance, whereas the second one depends on the variation of the charge population of the QD island, therefore causing changes in the overall capacitance.

As a matter of fact, rf-SETs have improved the sensitivity of an order of magnitude with respect to that of SETs and have been widely used to investigate QDs, ranging

from single shot measurements in rf-QPC [76], to spin and charge configuration of DQDs [77] and single Cooper pair transistors [74].

Finally, an alternative configuration of rf-SET is emerging: the gate coupled rf-SET. It consists in coupling a gate electrode to the resonant circuit. Despite the small capacitive coupling between the QD and the gate, external sources of dissipation, as for example the equivalent dielectric loss of the resonator, Sisyphus resistance [78] and strong quantum capacitance [79] allow for a readout with performances comparable to those of conventional rf-SETs [68] or rf-QPCs [79]. It turns out that, since  $R_{\rm eff} \ll Z_0$ , the loaded quality factor reduces to the unloaded one. Moreover as usually  $C_{\rm Q} \ll C_{\rm geom}$  the reflection coefficient near the resonance frequency becomes [74]:

$$\Gamma = -1 + 2iQ\left(\frac{C_{\rm Q}}{C_{\rm geom}}\right). \tag{2.26}$$

Therefore it results that the phase and the square modulus of  $\Gamma$  are respectively:

$$\theta = -2Q\left(\frac{C_{\rm Q}}{C_{\rm geom}}\right),\tag{2.27}$$

$$|\Gamma|^2 = 1 + 4Q^2 \left(\frac{C_{\rm Q}^2}{C_{\rm geom}^2}\right).$$

(2.28)

Such readout scheme has two major advantages with respect to rf-SETs. First it has been pointed out that rf-SETs are extremely sensitive to the exact position of the confining centre, so that in extreme cases only phenomena involving the drain, namely the reservoir coupled to the tank circuit, can be detected [80]. Conversely, in silicon nanotransistors the gate is placed just above the channel, ensuring a more symmetric sensitivity [80]. Secondly, even if rf-SETs have better performances than DC SETs, in terms of scalability there is no convenience in the use of an rf-SET [69] or rf-QPC [81] as external electrometers, since they complicate the structure of quantum devices. The gate readout scheme, by contrast, allows for compact structures since gates already in place to define the QD are exploited.

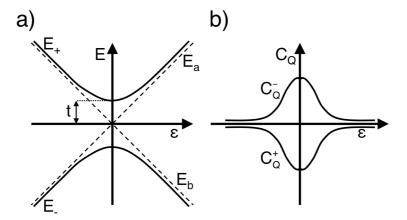

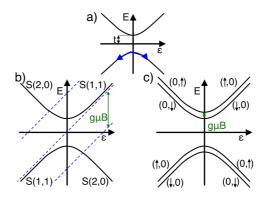

#### Effective capacitance in two-level systems

In the previous section the concept of the effective capacitance of a rf-SET has been introduced. Now I will explain it in more details. The radio-frequency reflectometry has been used to investigate two-level systems based on the charge state of a QD [68, 78] or the charge and spin state of a DQD [73, 82] and thanks to the scalability of the gate coupled scheme it is gaining interest as a tool for the readout of qubits states.

The charge confined in an island in a three terminal device, in which electrons can

**Figure 2.6:** a) Energy band diagram of a two-level system. b) Schematic representation of the quantum capacitance (third term of Equation 2.33) as a function of the detuning. As a consequence of the band curvature the quantum capacitance related to the ground term has positive value, whereas it is negative for the excited state.

tunnel in (out of) the island from two reservoirs and a gate tunes the electrochemical potential, can be expressed as [74]:

$$Q = \frac{(C_{\rm D} + C_{\rm S})C_{\rm G}}{C_{\Sigma}}V_{\rm G} - e\langle n \rangle \frac{C_{\rm G}}{C_{\Sigma}},\tag{2.29}$$

where  $C_{\Sigma}=C_{\rm S}+C_{\rm D}+C_{\rm G}$  is the total capacitance of the dot, due to the coupling with the electrodes, and  $\langle n \rangle$  is the average excess electrons number. Thereby the effective capacitance reads:

$$C_{\text{eff}} = \frac{dQ}{dV_{\text{G}}} = \frac{(C_{\text{D}} + C_{\text{S}})C_{\text{G}}}{C_{\Sigma}} - e\frac{d\langle n\rangle}{dV_{\text{G}}}\frac{C_{\text{G}}}{C_{\Sigma}},\tag{2.30}$$

or using the notation adopted previously  $C_{\rm eff} = C_{\rm geom} + C_{\rm Q}$ . As anticipated, the first term of Equation 2.30, or  $C_{\rm geom}$ , is a linear capacitive term which accounts for the couplings between the QD and the electrodes, whereas the second one,  $C_{\rm Q}$ , stems from variation in the QD population.

Now lets consider a general two-level system, as shown in Figure 2.6a, with unperturbed eigenstates  $E_a$ ,  $E_b$ . In presence of a purely non diagonal perturbation with real and equal off diagonal elements t, the two final eigenstates are [23]:

$$E_{\pm} = \pm \sqrt{\epsilon^2 + (2t)^2},$$

(2.31)

where -(+) labels the ground (excited) state and 2t is the energy gap at zero detuning ( $\epsilon = E_a - E_b$ ). The average electron occupation  $\langle n \rangle$  expresses the presence of an extra electron: in the single QD charge qubit this oscillates between 0 and

1; in DQDs the system oscillates between the charge configuration (2,0) and (1,1) or (1,0) and (0,1). It can be expressed as a function of the difference between the occupation probabilities of the two states  $Z = P_- - P_+$  [75]:

$$\langle n \rangle = \frac{1}{2} \left( 1 + \frac{\epsilon}{E_{+} - E_{-}} Z \right). \tag{2.32}$$

Thus  $C_{\rm eff}$ , with the assumption  $\epsilon = -e\alpha V_{\rm G}$ , becomes:

$$C_{\text{eff}} = C_{\text{geom}} + \frac{e^2 \alpha^2}{2} \left[ \frac{\epsilon}{E_+ - E_-} \frac{\partial Z}{\partial \epsilon} + Z \frac{(2t)^2}{(E_+ - E_-)^3} \right] = C_{\text{geom}} + C_{\text{T}} + C_{\text{Q}}.$$

(2.33)

From Equation 2.33 it emerges that the quantum capacitance has two distinct terms: the so called tunneling and the quantum capacitances, the second and the third terms respectively. The former is linked to processes of population redistribution, such as relaxation, whereas the latter is linked to the curvature of energy bands. The physical meaning of  $C_{\rm T}$  and  $C_{\rm Q}$  can be understood in terms of adiabatic and non adiabatic tunneling processes and population of the excited state. Two extremes cases are defined by the relation between the energy gap 2t and the rf photon energy  $h\nu$ :  $2t\gg h\nu$  or  $2t\ll h\nu$ . In the former case the photons do not have enough energy to excite the system to the higher energy level: the tunneling processes involve only the ground state. Therefore, the tunneling capacitance can be neglected and only the quantum capacitance survives [73, 82]. From equations 2.33 and 2.31 the quantum capacitance then can be rewritten as:

$$C_{\rm Q} = -(e\alpha)^2 \frac{\partial^2 E_{\pm}}{\partial \epsilon^2},\tag{2.34}$$

making evident that such term is proportional to the band curvature. As a results, it emerges that such capacitance can assume only positive values, reaching a maximum at zero detuning, as schematically depicted in Figure 2.6b.

On the other hand when  $2t \ll h\nu$  the excited state can be populated. In the limit of no gap, as in the case of transition between a single level and a continuum of states (i.e. dot-lead transitions), the quantum capacitance is negligible and only the tunnel capacitance is left. Moreover, three different regimes can be identified, depending on the relation between the tunneling rate  $\Gamma$  and  $\nu$ . When  $\Gamma \ll \nu$  there is no tunneling since the rf-drive is too fast; at high tunneling rate the tunneling is elastic: an electron tunnels out(in) the dot before a rf-cycle is completed. In both cases there is no dissipation and the reflected signal is almost zero. At the matching condition of  $\Gamma \approx \nu$  the tunneling is inelastic and the power dissipation is maximum, due to the Sisyphus effect [68, 78].

Finally, there is an intermediate case: non-adiabatic transition in presence of an energy gap. In this case  $h\nu\sim 2t$  and both terms are non-negligible. With the additional condition of  $\nu^{-1}< T_2$  the Landau-Zener-Stückelberg interference can

#### CHAPTER 2. OVERVIEW OF SILICON NANOELECTRONICS

| be observed [75] and the competition between the two terms leads to a capacitance that can assume both positive and negative sign. |

|------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

|                                                                                                                                    |

### **Chapter 3**

# Corner states in a single gate transistor: valley-based transport

In this chapter I report on the characterisation of a single gate nano-transistor. At 4.2 K two conductive paths appear at the edges of the channel: two quantum dots are present. The absence of a second gate prevents independently addressing the two dots. Nevertheless one of them, assisted by a single donor, is in the strong coupling regime. This condition allows for the investigation of the Kondo-perturbed regime in the first spin-valley shell. At single occupancy the transport is influenced by the conservation of the valley parity index during tunneling. 1

#### 3.1 Introduction

In the attempt to further reduce the transistors dimensions, in particular the channel length, non-planar solutions have been adopted. Different geometries have been reported to minimise short channel effects and ensure high on-current: Fin-FETs [83], tri-gate [84],  $\Pi$ -gate [85] and  $\Omega$ -gate SOI MOSFETs [86]. In such transistors a silicon nanowire connects the two reservoirs (i.e. source and drain) and a second nanowire, namely the gate, wraps the first one on three sides. Both in tri-gate structures [87, 88, 89] and FinFETs [28, 83] it has been shown that conductive paths form at the topmost corners of the channel. Here the electric field from two adjacent sides of the gate is maximum, producing the accumulation of the carriers. Spacers around the gate [90], charged defects at the interface between silicon and gate oxide or in the oxide and surface roughness [28, 68, 91] generate potential barriers leading to the formation of two quantum dots, one per corner.

<sup>&</sup>lt;sup>1</sup>This chapter has been partly adapted from A. Crippa, M. L. V. Tagliaferri, D. Rotta, M. De Michielis, G. Mazzeo, M. Fanciulli, R. Wacquez, M. Vinet and E. Prati, "Valley blockade and multielectron spin-valley Kondo effect in silicon", *Physical Review B*, **92**(3):035424, 2015.

# CHAPTER 3. CORNER STATES IN A SINGLE GATE TRANSISTOR: VALLEY-BASED TRANSPORT

In such devices the DQD can be fully controlled by means of an additional gate, which can be provided by using the substrate as a back gate [92] or by etching of the top gate in split-gate devices [73].

Here I report on a single gate device with tri-gate structure in which two quantum dots form at the corners. In this case, due to the original setup (see Chapter 6 for its development), the back gate was not polarised thus preventing a full tunability of the double dot system. Nonetheless, one of the two quantum dots happens to be in strong coupling regime with the leads. It is therefore possible to investigate second order transport [3, 36, 93]. In strong coupling regime, in fact, tunneling rates are sufficiently high for an electron to tunnel in(out) and another out(in) of a quantum dot in a time  $t \lesssim \tau$  even when first order tunnel should be blocked, where  $\tau$  is the lifetime of the virtual state. Second-order tunneling processes are called cotunneling, since two electrons are involved [94, 95]. For that reason, cotunneling has been regarded as a limiting mechanism for single electron devices [96, 97, 98]. In early works cotunneling was investigated in metallic regime, where the discreteness of the levels can be neglected, in accordance to the theoretical works [94, 99]. Depending on the final dot state two different types of processes are identified [3, 94]: cotunneling is defined as elastic if the final state corresponds to the initial one, otherwise as inelastic. When the energy spacing,  $\Delta$ , between ground and first excited state is no more negligible, the manifestation of cotunneling changes. In this regime [100, 101, 102], when the bias voltage supplies this energy amount, inelastic cotunneling is allowed and conduction areas appear inside a Coulomb diamond [3, 36]. Inelastic cotunneling has been proposed as a tool for excited states spectroscopy, involving orbital [36, 103] or spin states [104]. An ordered and coherent repetition of spin-flip cotunneling events, involving the spin of a localised electron coupled to a many-body spin state of conduction electrons, gives rise to Kondo effect in III-V quantum dots [45, 46, 105].

The 6-fold valley degeneracy of bulk silicon is broken at the nanoscale [3], leading to an enriched phenomenology with respect to physical effects studied in III-V compounds, since single particle levels are further identified by the valley parity quantum number. Valley-related effects have been lately reported, from the valley filling sequence in silicon quantum dots [106, 107, 108] and lifetime-enhanced transport as indirect observation of spin and valley blockade [109], to a valley Kondo effect in silicon quantum dots [110] or in an As atom at single electron filling [19, 111]. The Kondo effect manifestation, when related to valley parity index, is more complex than in spin- $\frac{1}{2}$  Kondo effect [48, 53, 54]. In fact the valley parity index [112, 113] acts as a pseudo spin [35, 114], giving an additional degree of freedom which can be screened by conduction electrons and allowing for highly symmetric SU(4) Kondo states [44].

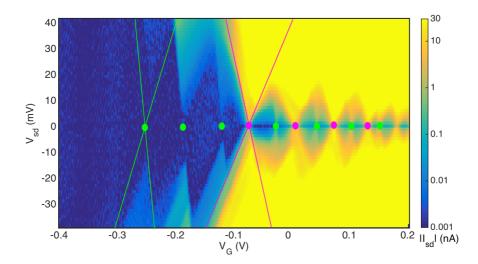

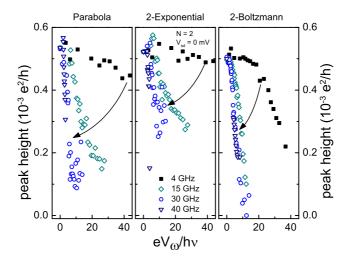

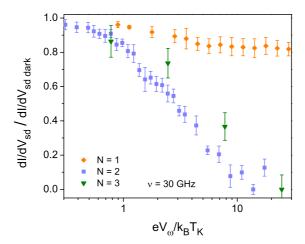

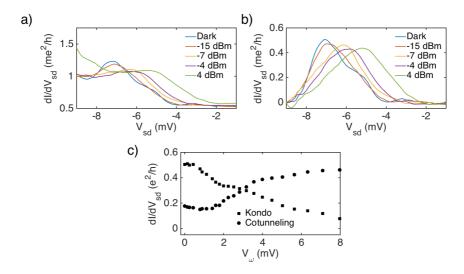

In this chapter I focus on peculiarities of valley dependent quantum transport both in sequential and second order tunneling processes. The conservation of valley parity index during tunneling leads to asymmetries in the Coulomb diamonds at single occupation. The manifestation of Kondo effect reflects the fourfold degeneracy due to spin and valley: at 4.2 K the Kondo-perturbed regime appears for the first three electrons. Here coherent Kondo effect coexists with inelastic cotunneling [36, 115], which is observed in consecutive Coulomb diamonds. In agreement with theory, standard Coulomb blockade is observed at N=4 where Kondo effect is forbidden. Temperature and microwave irradiation act on these second order processes, allowing to recognise the different nature of the tunneling phenomena. In fact, they destroy the spin-correlation of Kondo effect [45, 52, 116], whereas they strengthen inelastic cotunneling [99, 117, 118]. Microwave irradiation and temperature can switch the system from a Kondo-perturbed regime to an inelastic cotunneling one, as already demonstrated for the magnetic field induced crossover [47, 104].

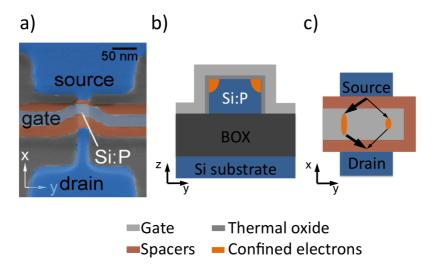

#### 3.2 Device fabrication

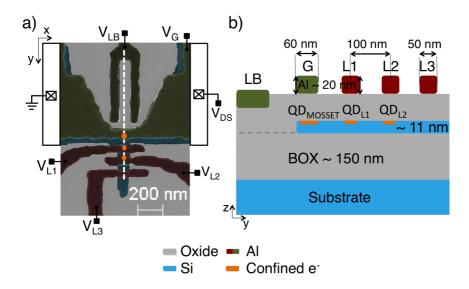

The device under investigation is a tri-gate FET fabricated from fully depleted silicon-on-insulator (FDSOI) technology. In Figure 3.1a a Scanning Electron Micrograph (SEM) image of a device with the same tri-gate structure as the one investigated here is shown. The active region of the device is defined by etching the phosphorus implanted ( $10^{18}~\rm cm^{-3}$ ) silicon layer of the SOI substrate. As a result a 50 nm large and 8 nm thick channel connects the source and the drain contacts. Perpendicularly to it a 20 nm large gate, with a 5 nm thermal SiO<sub>2</sub> of isolation, is then grown, covering the three exposed faces. Silicon nitride (Si<sub>3</sub>N<sub>4</sub>) spacers around the gate protect the active region from arsenic implantation of highly doped (metal-like) source-drain electrodes. The active area of the channel is the region covered by the gate and the other portions of the nanowire behave as extensions of the contacts. In Figure 3.1b and c the likely position of the two quantum dots is shown in a schematic cross section perpendicular to the transport direction and in a schematic top view of the channel.

#### 3.3 Device characterisation

Transport measurements have been performed at 4.2 K by immersion of the device in liquid  $^4$ He at atmospheric pressure. The device was connected to a multistage room temperature transimpedance amplifier. In this configuration the source is grounded while the drain is connected to the inverting input of amplifier. Connecting the non-inverting input to the NI-PXI-6733 the drain can be controlled by virtual mass. The selected amplifier has a current noise of 1  $\mu A$  rms at full bandwidth, which is 16 kHz. The gate is connected to the same NI-PXI-6733 module. For conductance measurements standard lock-in technique is used, applying an excitation of 40  $\mu$ V at 116 Hz to the source contact. The microwave irradiation, with

**Figure 3.1:** Architecture of the device. a) SEM image of a device with the same structure as the tested one. b) Sketch of the cross-section of the channel perpendicular to the transport direction. Near threshold two quantum dots form at the topmost corners. c) The two conductive paths are depicted in the sketch of the top view parallel to the transport direction. The thicker (thinner) arrows refer to the strong (weak) coupled quantum dot.

1–40 GHz continuous-wave, is provided by a beryllium in stainless-steel coaxial line (UT-141), with a diameter of 3.5 mm, ending with an unmatched dipolar antenna [52, 119].

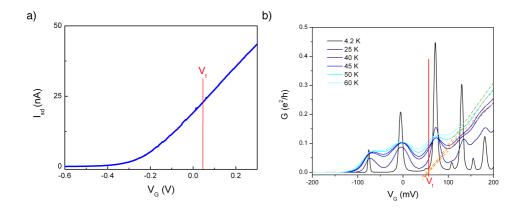

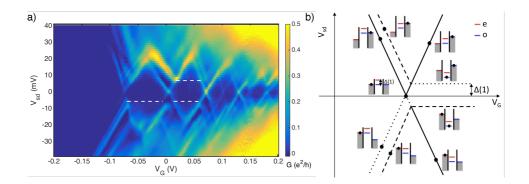

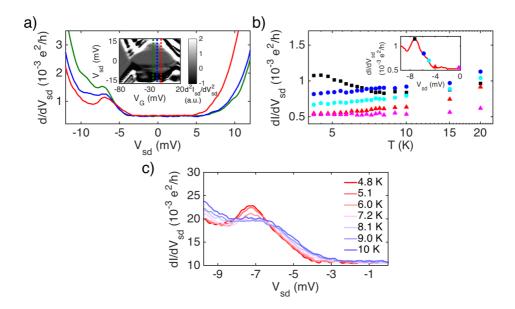

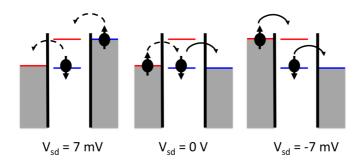

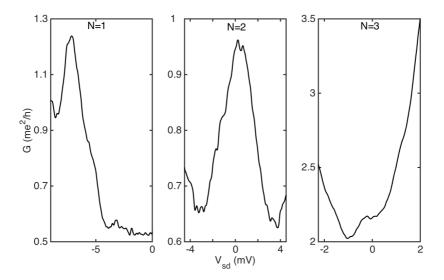

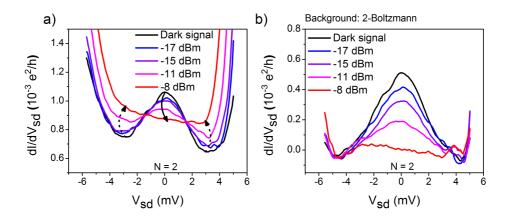

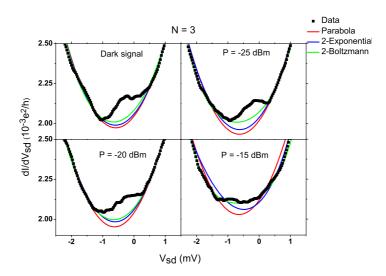

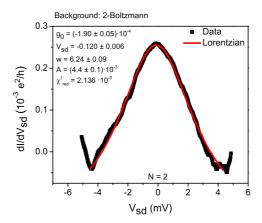

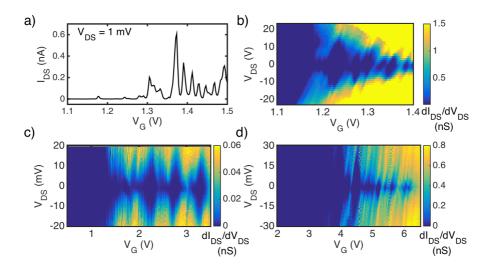

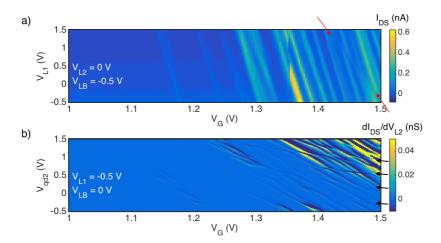

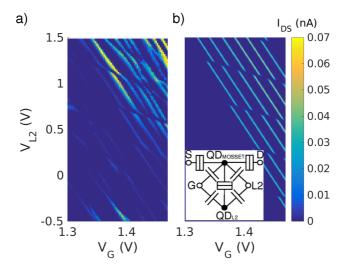

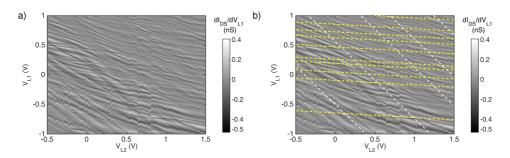

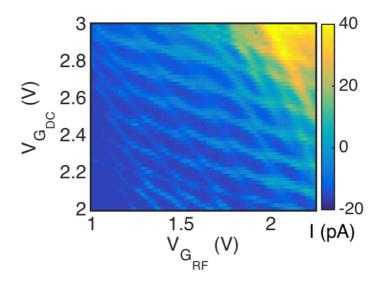

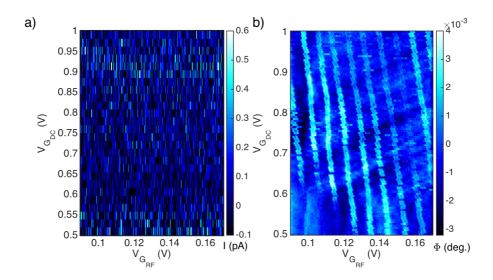

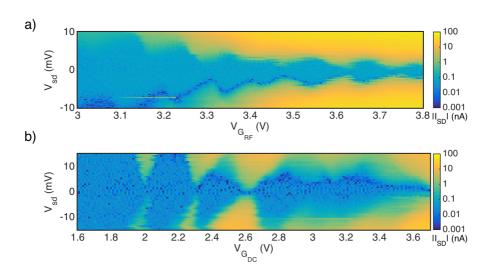

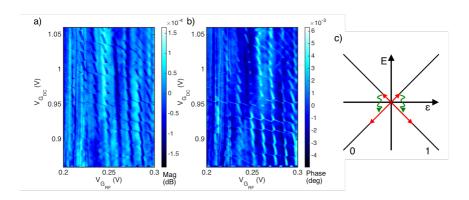

#### 3.3.1 Quantum transport at the corners